FlexRay Module (FLEXRAYV4)

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 113

NOTE

If the counter has reached its maximum value 0xFFFF and is in the

multicycle mode (SSCCRn[MCY] equaling 1), the counter is not reset to

0x0000. The application can reset the counter by clearing the

SSCCRn[MCY] bit and waiting for the next cycle start, when the FlexRay

module clears the counter. Subsequently, the counter can be set into the

multicycle mode again.

3.3.2.46 MTS A Configuration Register (MTSACFR)

This register controls the transmission of the Media Access Test Symbol MTS on channel A. For more

details, see Section 3.4.13, “MTS Generation”.

3.3.2.47 MTS B Configuration Register (MTSBCFR)

Table 3-55. SSCR0–SSCR3 Field Descriptions

Field Description

15–0

SLOTSTATUSCNT

Slot Status Counter — This field provides the current value of the Slot Status Counter.

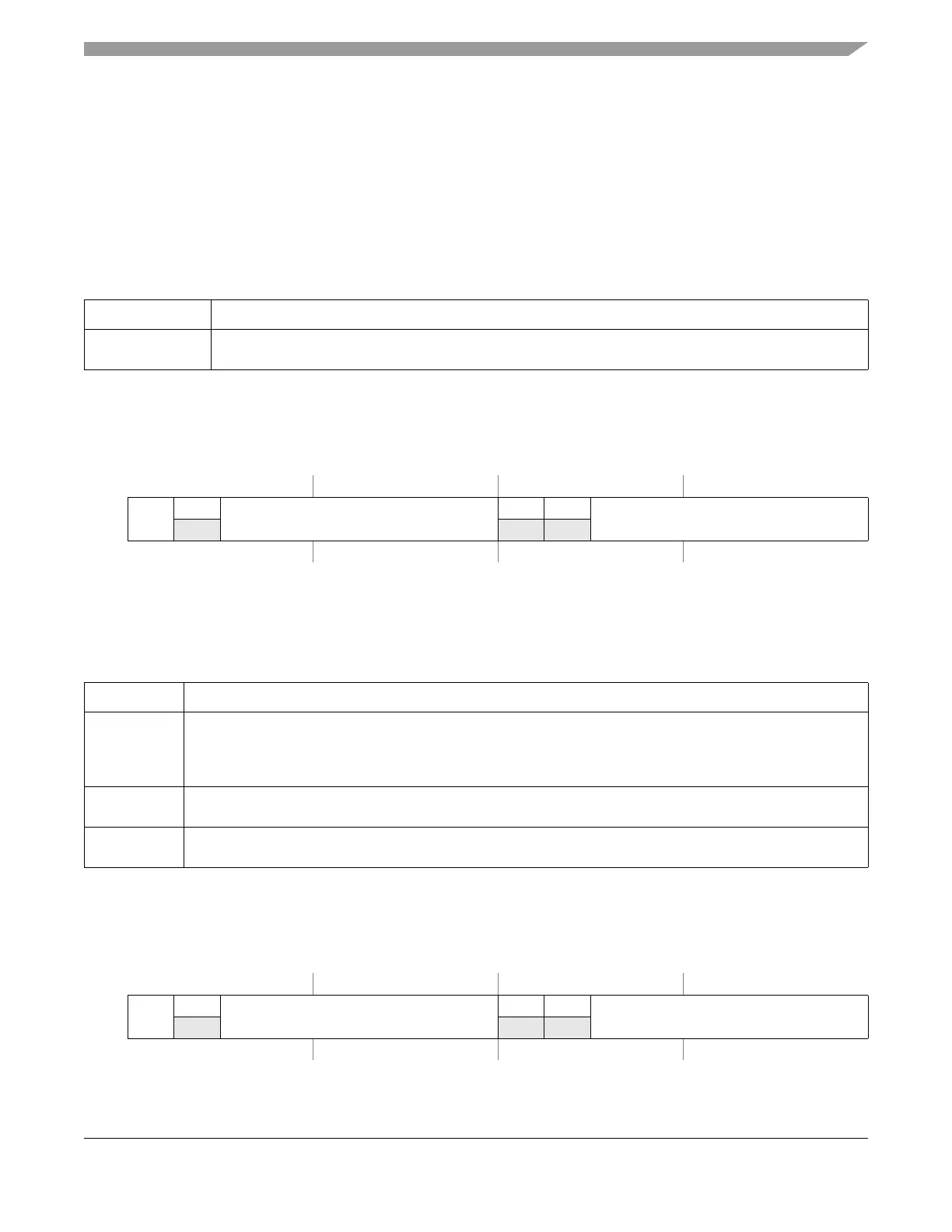

0x0080 Write: MTE: Any Time

CYCCNTMSK, CYCCNTVAL: POC:config

1514131211109876543210

R

MTE

0

CYCCNTMSK

00

CYCCNTVAL

W

Reset0000000000000000

Figure 3-45. MTS A Configuration Register (MTSACFR)

Table 3-56. MTSACFR Field Descriptions

Field Description

15

MTE

Media Access Test Symbol Transmission Enable — This control bit is used to enable and disable the

transmission of the Media Access Test Symbol in the selected set of cycles.

0 MTS transmission disabled

1 MTS transmission enabled

13–8

CYCCNTMSK

Cycle Counter Mask — This field provides the filter mask for the MTS cycle count filter.

5–0

CYCCNTVAL

Cycle Counter Value — This field provides the filter value for the MTS cycle count filter.

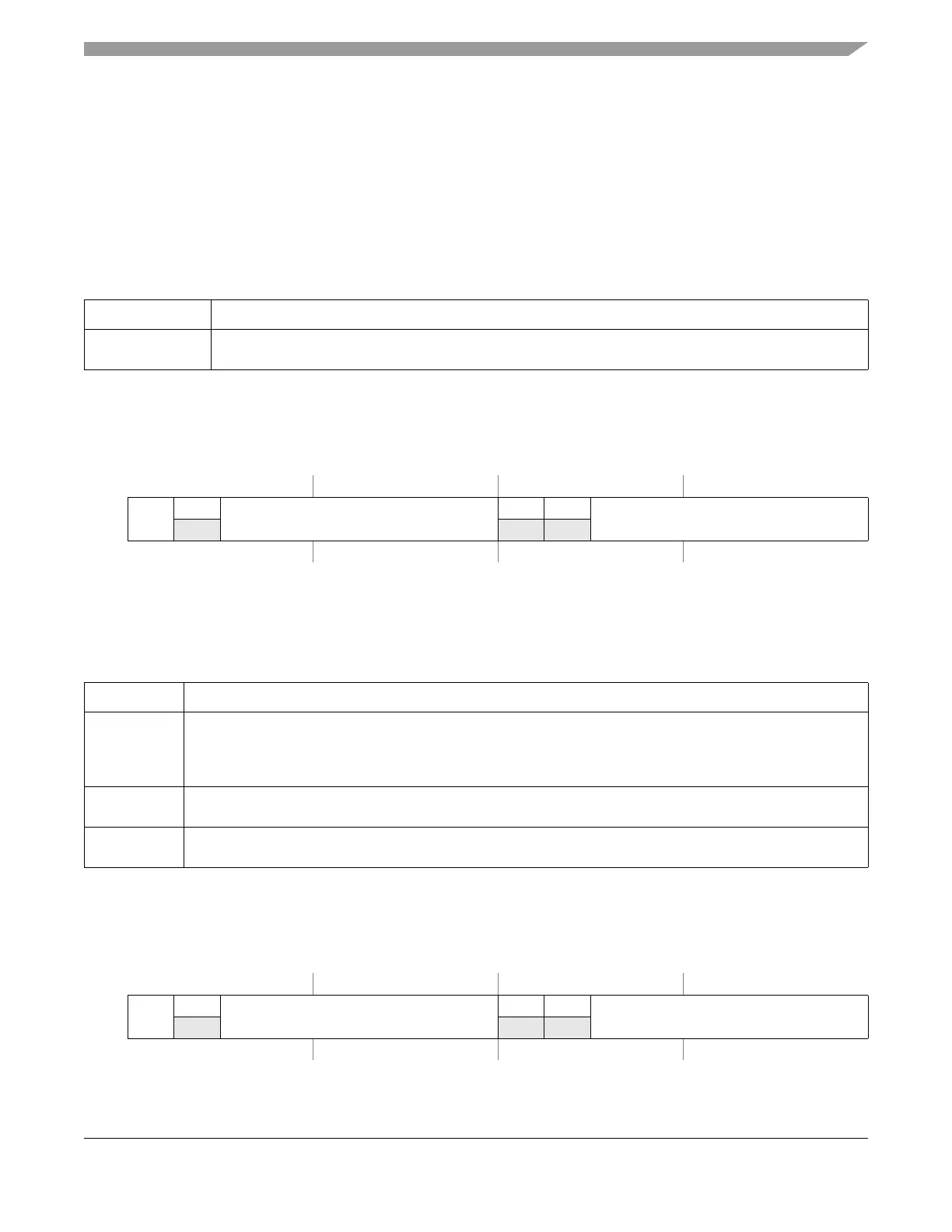

0x0082 Write: MTE: Any Time

CYCCNTMSK, CYCCNTVAL: POC:config

1514131211109876543210

R

MTE

0

CYCCNTMSK

00

CYCCNTVAL

W

Reset0000000000000000

Figure 3-46. MTS B Configuration Register (MTSBCFR)

Loading...

Loading...