FlexRay Module (FLEXRAYV4)

MFR4310 Reference Manual, Rev. 2

110 Freescale Semiconductor

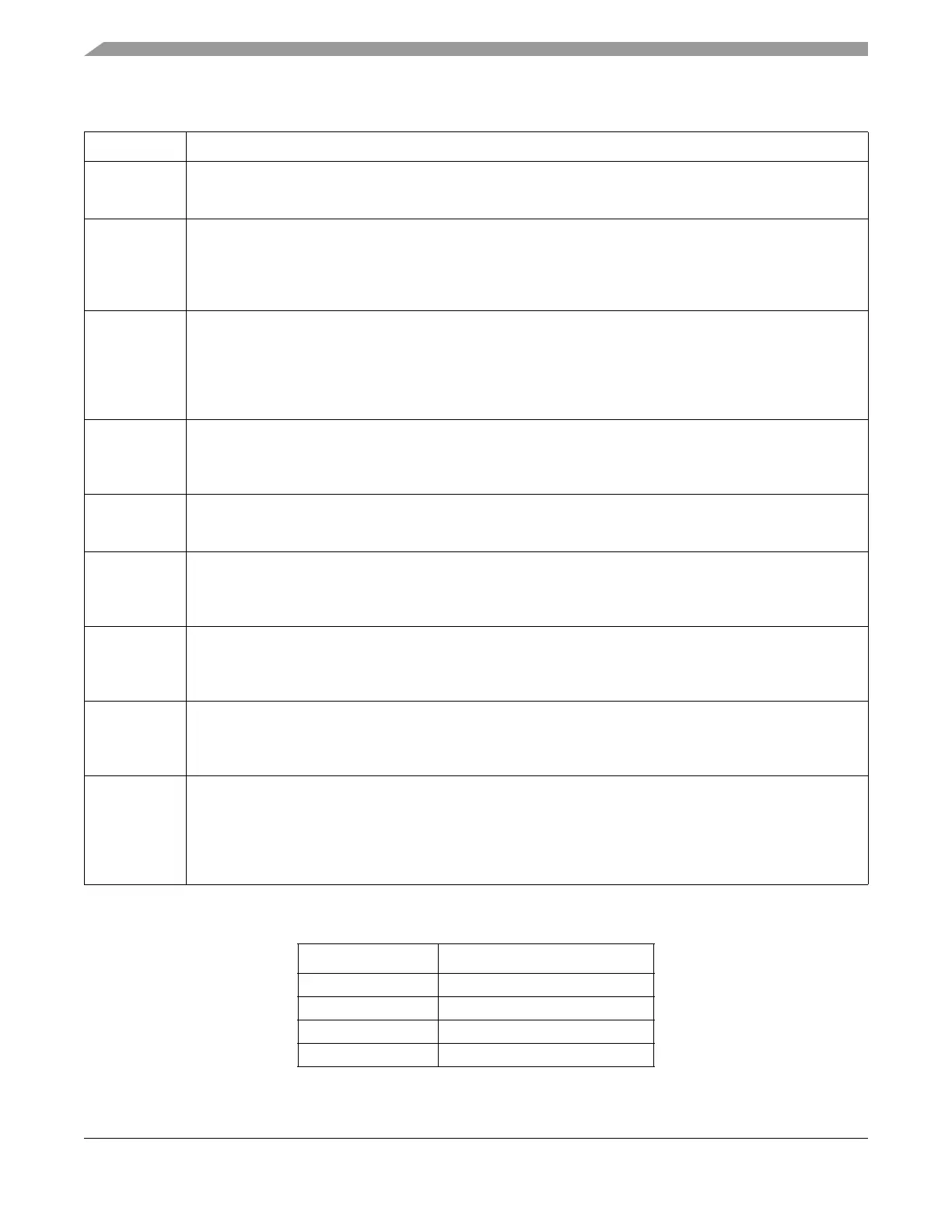

Table 3-52. SSCCR Field Descriptions

Field Description

15

WMD

Write Mode — This control bit defines the write mode of this register.

0 Write to all fields in this register on write access.

1 Write to SEL field only on write access.

13–12

SEL

Selector — This field selects one of the four internal slot counter condition registers for access.

00 select SSCCR0.

01 select SSCCR1.

10 select SSCCR2.

11 select SSCCR3.

10–9

CNTCFG

Counter Configuration — These bit field controls the channel related incrementing of the slot status counter.

00 increment by 1 if condition is fulfilled on channel A.

01 increment by 1 if condition is fulfilled on channel B.

10 increment by 1 if condition is fulfilled on at least one channel.

11 increment by 2 if condition is fulfilled on both channels channel.

increment by 1 if condition is fulfilled on only one channel.

8

MCY

Multi Cycle Selection — This bit defines whether the slot status counter accumulates over multiple

communication cycles or provides information for the previous communication cycle only.

0 The Slot Status Counter provides information for the previous communication cycle only.

1 The Slot Status Counter accumulates over multiple communication cycles.

7

VFR

Valid Frame Restriction — This bit is used to restrict the counter to received valid frames.

0 The counter is not restricted to valid frames only.

1 The counter is restricted to valid frames only.

6

SYF

Sync Frame Restriction — This bit is used to restrict the counter to received frames with the sync frame

indicator bit set to 1.

0 The counter is not restricted with respect to the sync frame indicator bit.

1 The counter is restricted to frames with the sync frame indicator bit set to 1.

5

NUF

Null Frame Restriction — This bit is used to restrict the counter to received frames with the null frame

indicator bit set to 0.

0 The counter is not restricted with respect to the null frame indicator bit.

1 The counter is restricted to frames with the null frame indicator bit set to 0.

4

SUF

Startup Frame Restriction — This bit is used to restrict the counter to received frames with the startup frame

indicator bit set to 1.

0 The counter is not restricted with respect to the startup frame indicator bit.

1 The counter is restricted to received frames with the startup frame indicator bit set to 1.

3–0

STATUSMASK

Slot Status Mask — This bit field is used to enable the counter with respect to the four slot status error

indicator bits.

STATUSMASK[3] – This bit enables the counting for slots with the syntax error indicator bit set to 1.

STATUSMASK[2] – This bit enables the counting for slots with the content error indicator bit set to 1.

STATUSMASK[1] – This bit enables the counting for slots with the boundary violation indicator bit set to 1.

STATUSMASK[0] – This bit enables the counting for slots with the transmission conflict indicator bit set to 1.

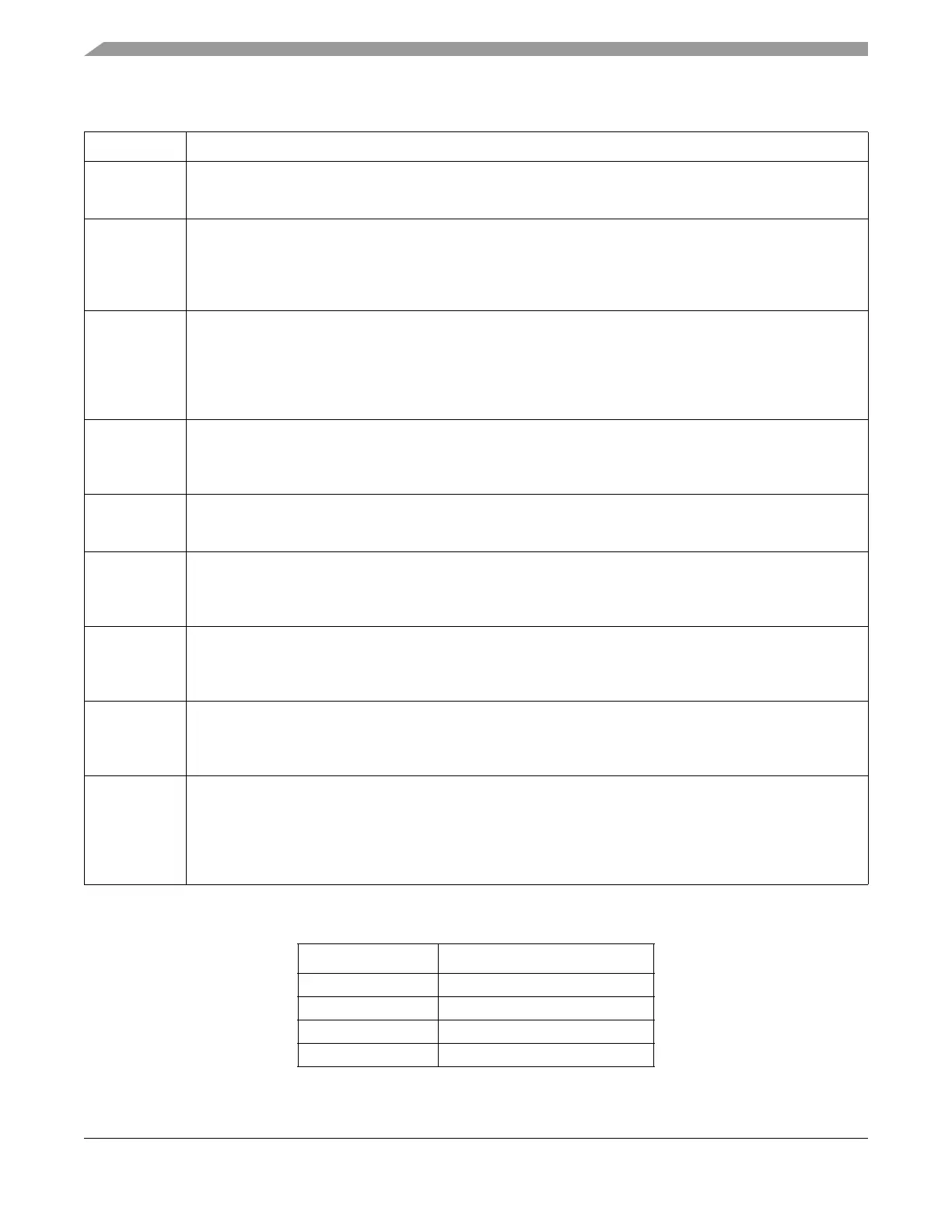

Table 3-53. Mapping between internal SSCCRn and SSCRn

Condition Register Condition Defined for Register

SSCCR0 SSCR0

SSCCR1 SSCR1

SSCCR2 SSCR2

SSCCR3 SSCR3

Loading...

Loading...