Clocks and Reset Generator (CRG)

MFR4310 Reference Manual, Rev. 2

228 Freescale Semiconductor

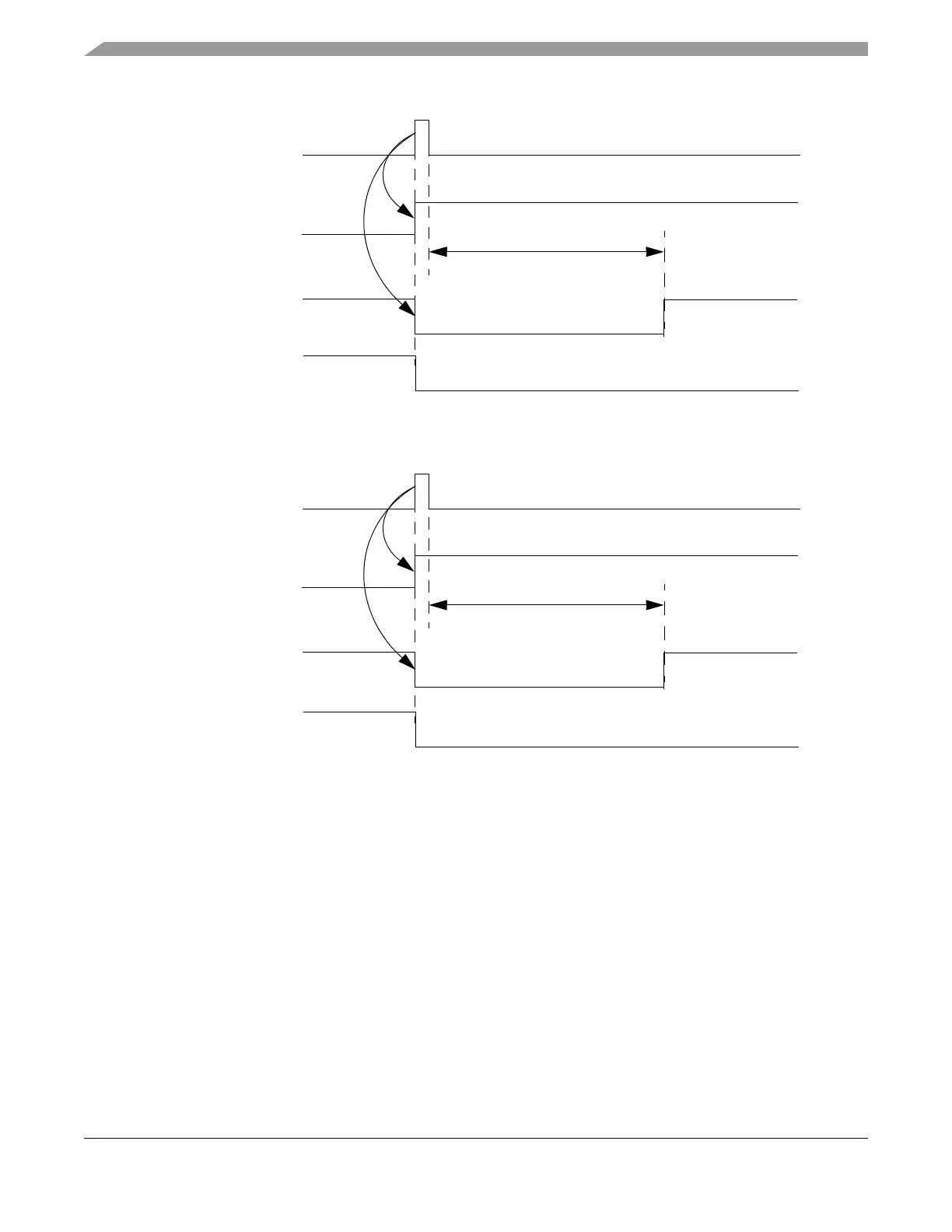

Figure 6-4. Low Voltage Reset

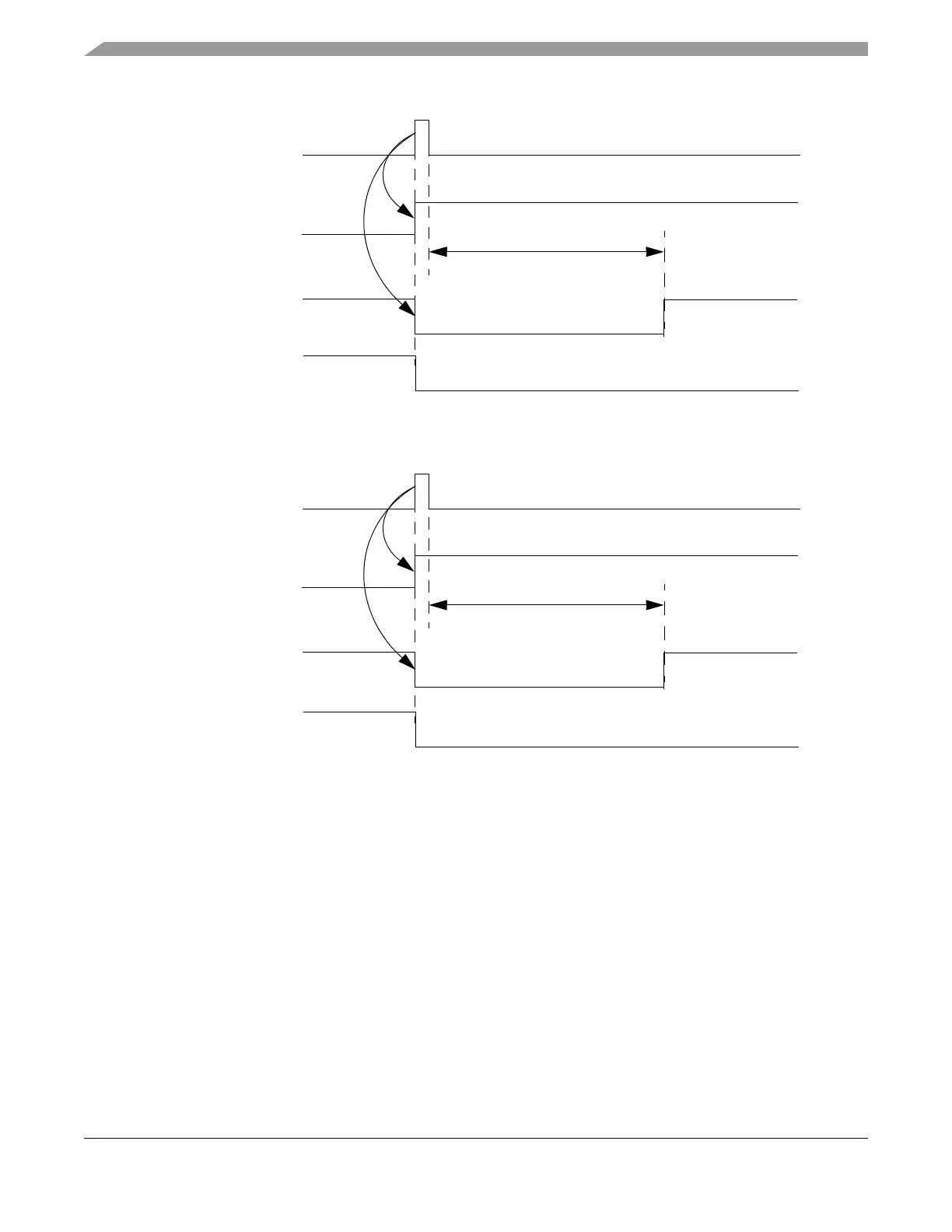

Figure 6-5. Clock Monitor Failure Reset

6.4.1.3 External Reset

When the RESET# signal is asserted the CRG asserts the system reset signal. The CRG deasserts the

system reset signal approximately 70 EXTAL/CLK_CC clock periods after the deassertion of the RESET#.

The CRG asserts the INT_CC# interrupt line and the external reset interrupt flag, CRSR.ERIF, on the

assertion of the RESET# signal.

NOTE

The CRG deasserts the INT_CC# signal when CRSR.PRIF, CRSR.LVIF,

CRSR.CMIF and CRSR.ERIF bits are 0.

Figure 6-6 illustrates an external reset scheme.

low voltage reset

system reset

~16420 EXTAL/CLK_CC periods

CRSR.LVIF

INT_CC#

clock monitor failure

system reset

~16420 EXTAL/CLK_CC periods

CRSR.CMIF

(if enabled)

INT_CC#

Loading...

Loading...