FlexRay Module (FLEXRAYV4)

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 141

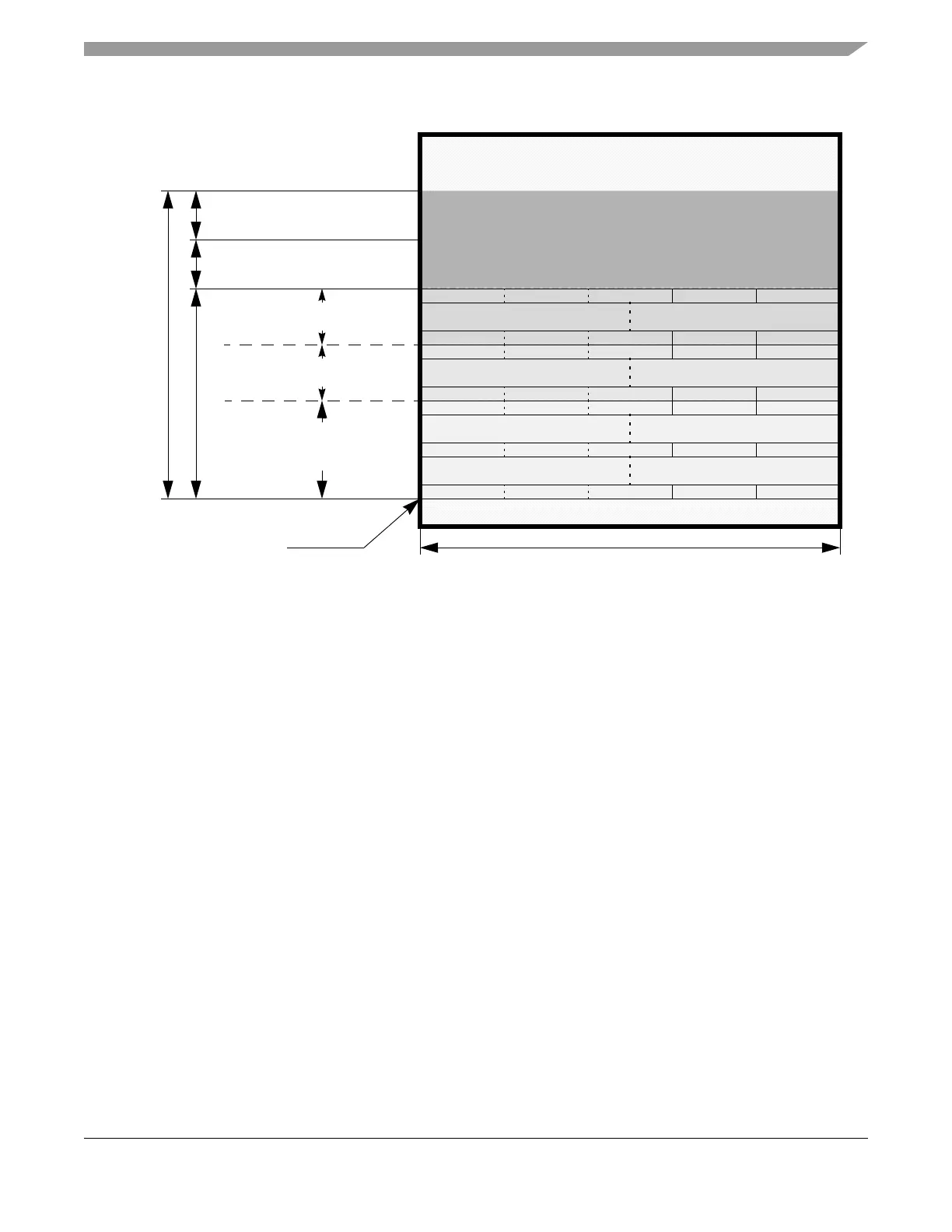

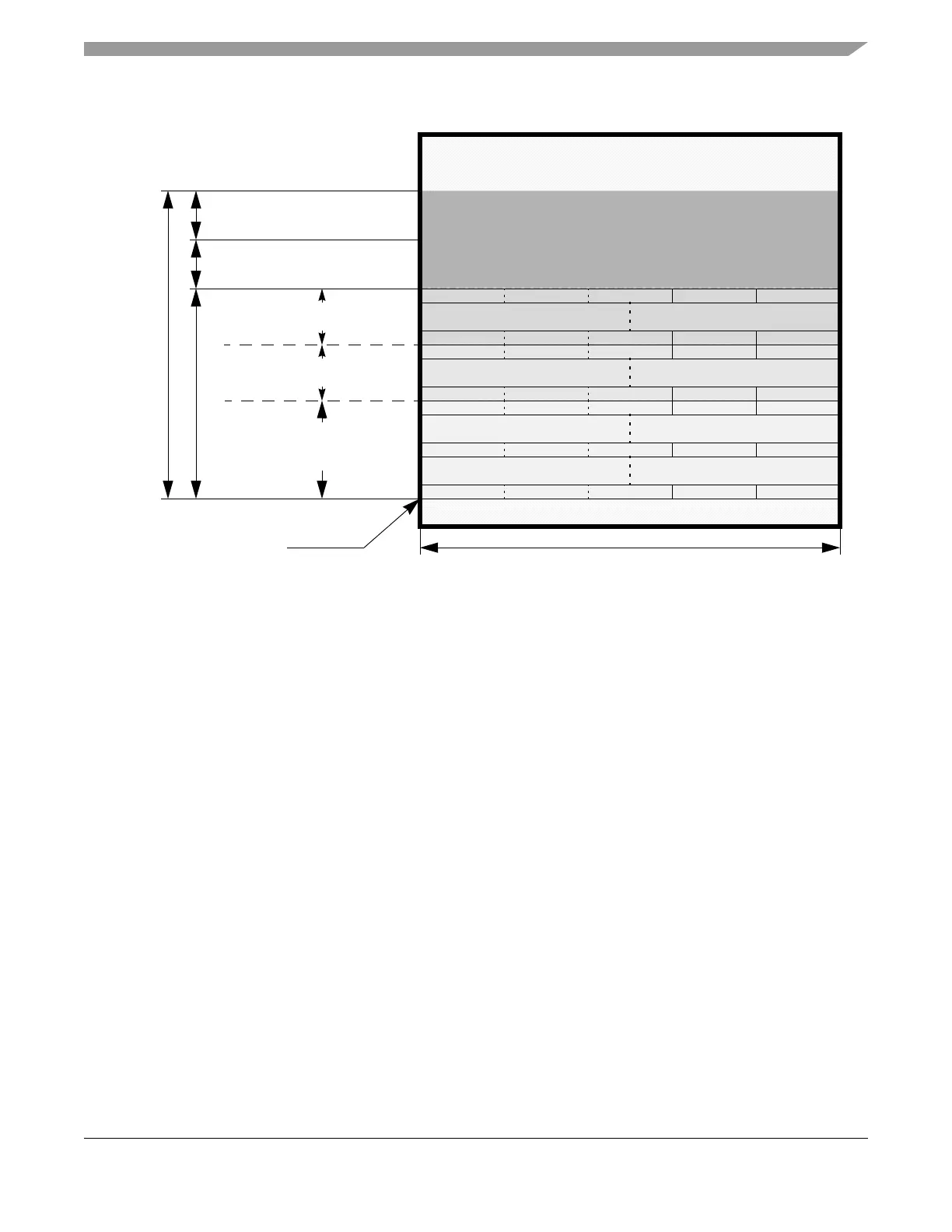

Figure 3-100. Example of FRM Layout

3.4.4.1 Message Buffer Header Area

The message buffer header area contains all message buffer header fields of the physical message buffers

for all message buffer types. The following rules apply to the message buffer header fields for the three

type of message buffers.

1. The start address SADR_MBHF of each message buffer header field for individual message

buffers and receive shadow buffers must fulfill Equation 3-6.

SADR_MBHF = (i * 10) + 0x800; (0 <= i < 256) Eqn. 3-6

2. The start address SADR_MBHF of each message buffer header field for the receive FIFO must

fulfill Equation 3-7.

SADR_MBHF = (i * 10) + 0x800; (0 <= i < 256) Eqn. 3-7

3. The message buffer header fields for a receive FIFO have to be a contiguous area.

3.4.4.2 Message Buffer Data Area

The message buffer data area contains all the message buffer data fields of the physical message buffers.

Each message buffer data field must start at a 16-bit boundary.

Message Buffer Header Area

FRM

Message Buffer Data Area

Sync Frame Table Area

Data Field OffsetFrame Header Slot Status

Data Field OffsetFrame Header Slot Status

Message Buffer Header Fields

Individual Message Buffers

Receive Shadow Buffers

Data Field OffsetFrame Header Slot Status

Data Field OffsetFrame Header Slot Status

Message Buffer Header Fields

Receive FIFO A

Data Field OffsetFrame Header Slot Status

Data Field OffsetFrame Header Slot Status

Message Buffer Header Fields

Receive FIFO B

Data Field OffsetFrame Header Slot Status

10 bytes

0x800

Device Memory

Loading...

Loading...