FlexRay Module (FLEXRAYV4)

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 85

3.3.2.13 Protocol Interrupt Enable Register 1 (PIER1)

This register defines whether or not the individual interrupt flags defined in Protocol Interrupt Flag

Register 1 (PIFR1) can generate a protocol interrupt request.

4

TBVB_IE

Transmission across boundary on channel B Interrupt Enable — This bit controls TBVB_IF interrupt request

generation.

0 interrupt request generation disabled

1 interrupt request generation enabled

3

TBVA_IE

Transmission across boundary on channel A Interrupt Enable — This bit controls TBVA_IF interrupt request

generation.

0 interrupt request generation disabled

1 interrupt request generation enabled

2

TI2_IE

Timer 2 Expired Interrupt Enable — This bit controls TI1_IF interrupt request generation.

0 interrupt request generation disabled

1 interrupt request generation enabled

1

TI1_IE

Timer 1 Expired Interrupt Enable — This bit controls TI1_IF interrupt request generation.

0 interrupt request generation disabled

1 interrupt request generation enabled

0

CYS_IE

Cycle Start Interrupt Enable — This bit controls CYC_IF interrupt request generation.

0 interrupt request generation disabled

1 interrupt request generation enabled

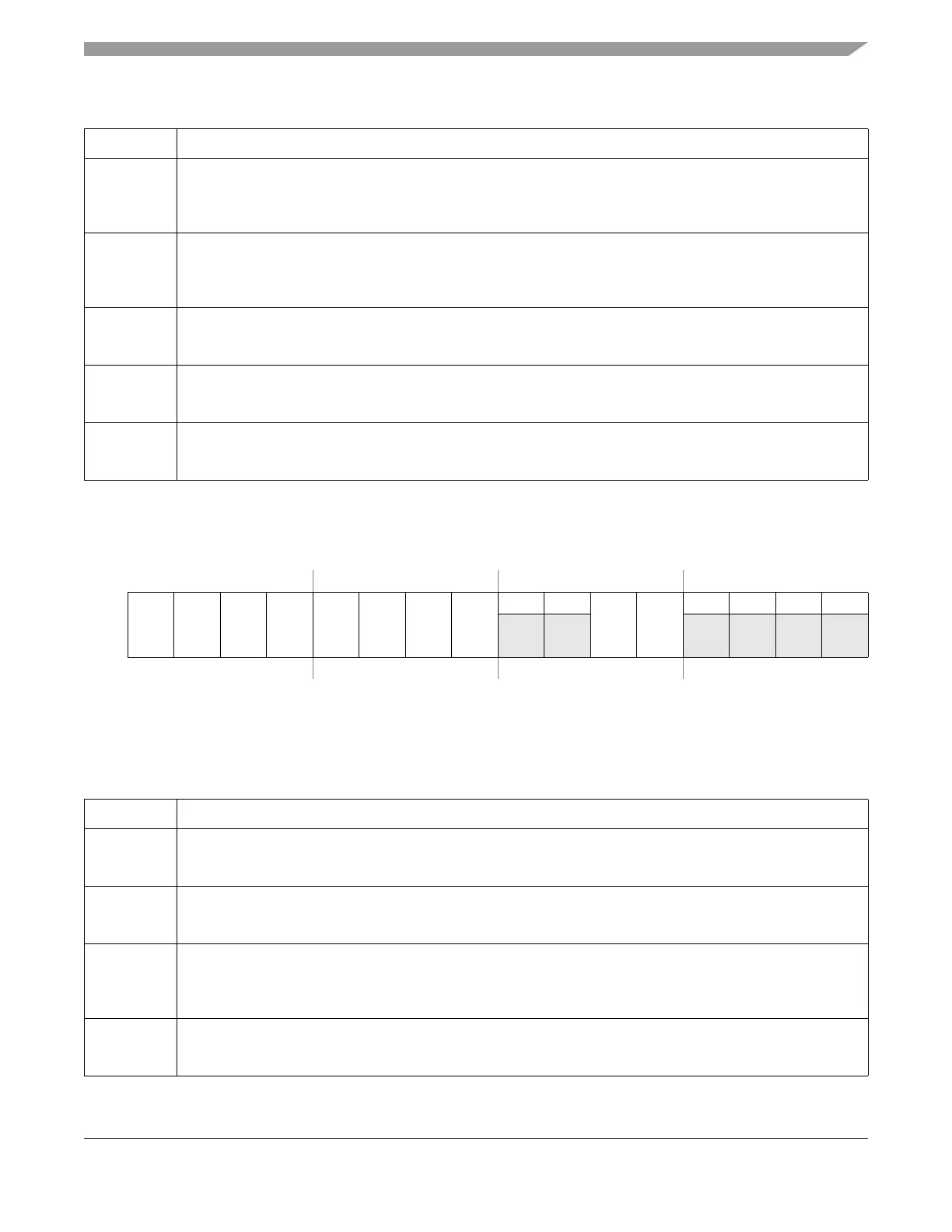

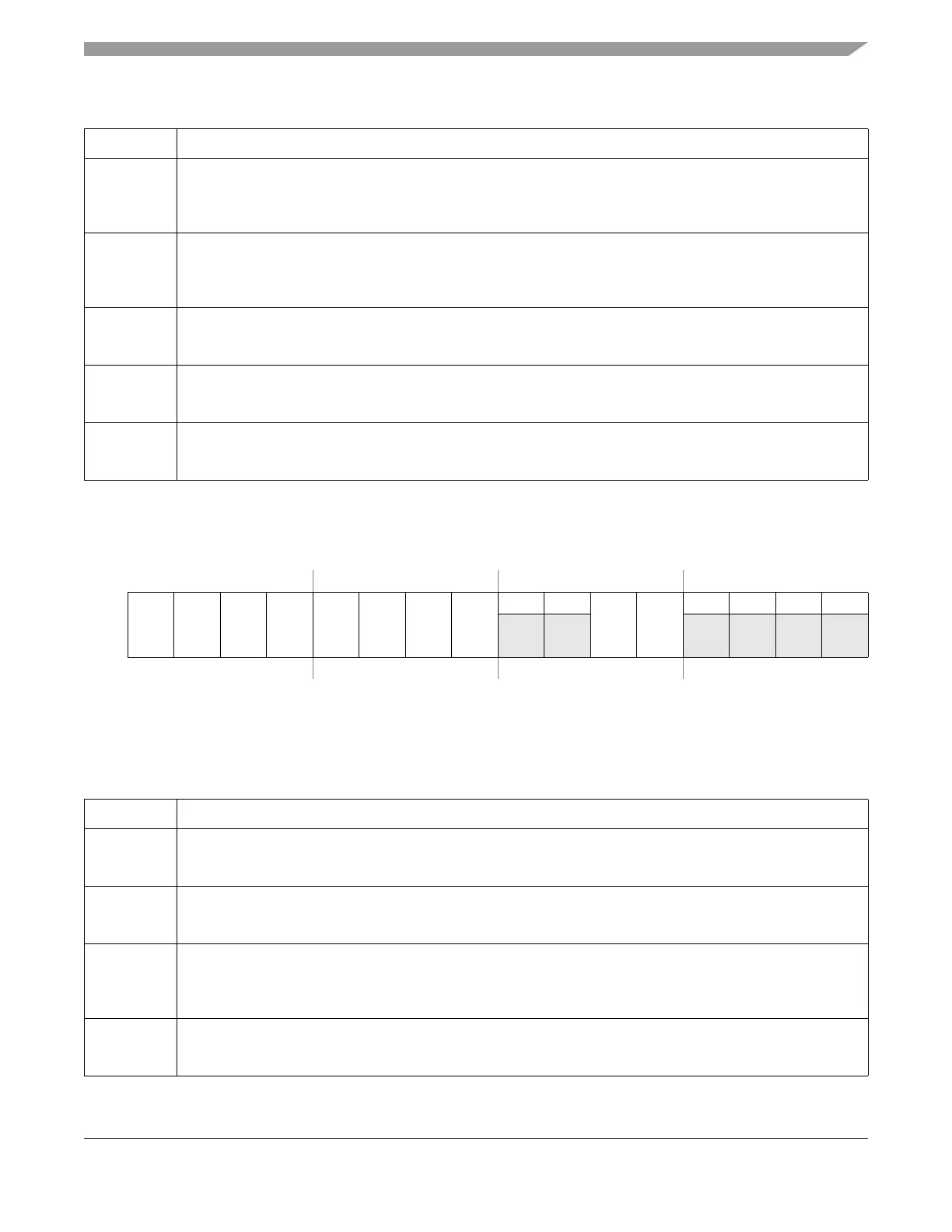

0x001E Write: Any Time

1514131211109876543210

R

EMC_IE

IPC_IE

PECF_IE

PSC_IE

SSI3_IE

SSI2_IE

SSI1_IE

SSI0_IE

00

EVT_IE

ODT_IE

0000

W

Reset0000000000000000

Figure 3-12. Protocol Interrupt Enable Register 1 (PIER1)

Table 3-20. PIER1 Field Descriptions

Field Description

15

EMC_IE

Error Mode Changed Interrupt Enable — This bit controls EMC_IF interrupt request generation.

0 interrupt request generation disabled

1 interrupt request generation enabled

14

IPC_IE

Illegal Protocol Control Command Interrupt Enable — This bit controls IPC_IF interrupt request generation.

0 interrupt request generation disabled

1 interrupt request generation enabled

13

PECF_IE

Protocol Engine Communication Failure Interrupt Enable — This bit controls PECF_IF interrupt request

generation.

0 interrupt request generation disabled

1 interrupt request generation enabled

12

PSC_IE

Protocol State Changed Interrupt Enable — This bit controls PSC_IF interrupt request generation.

0 interrupt request generation disabled

1 interrupt request generation enabled

Table 3-19. PIER0 Field Descriptions (Continued)

Field Description

Loading...

Loading...