Clocks and Reset Generator (CRG)

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 227

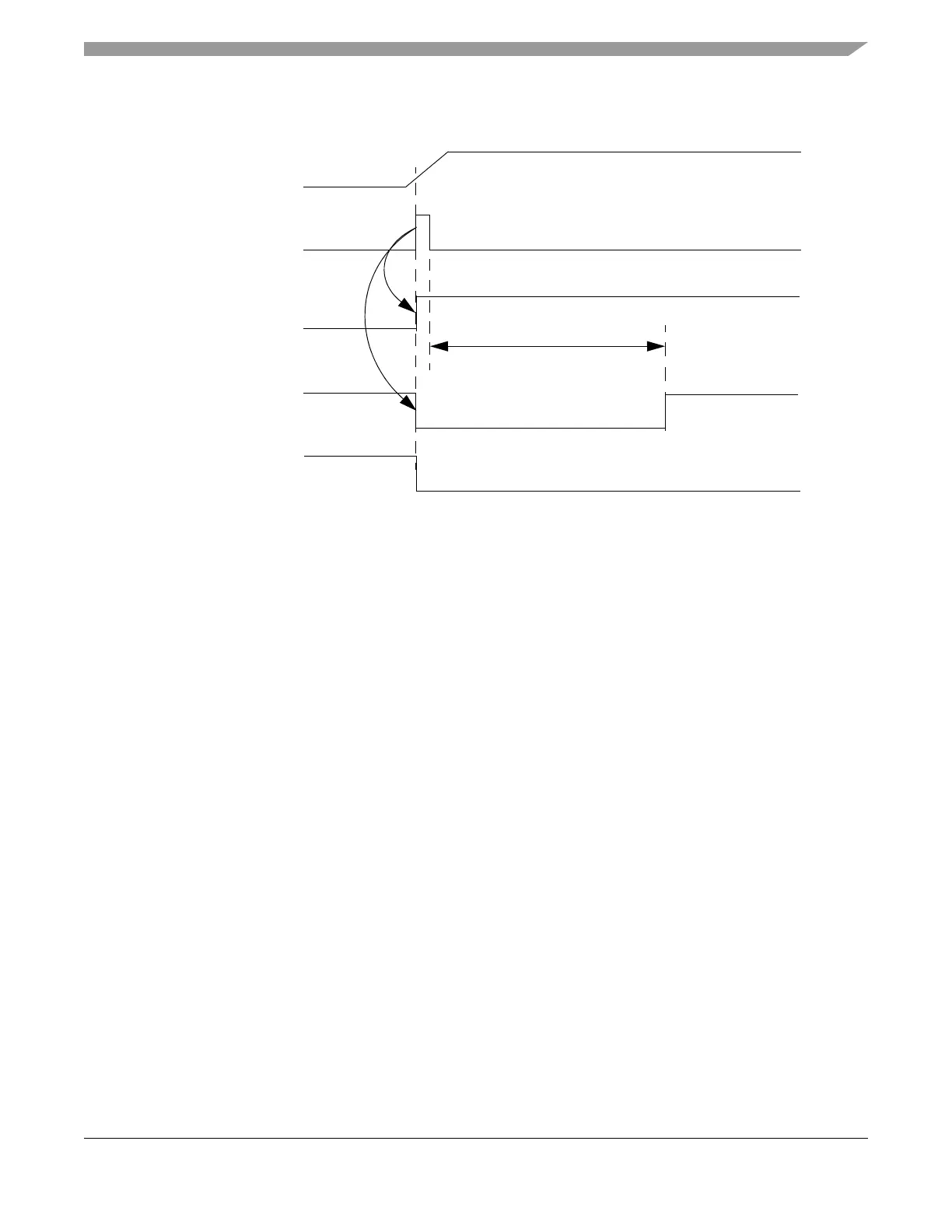

Figure 6-3. CRG Power On Reset

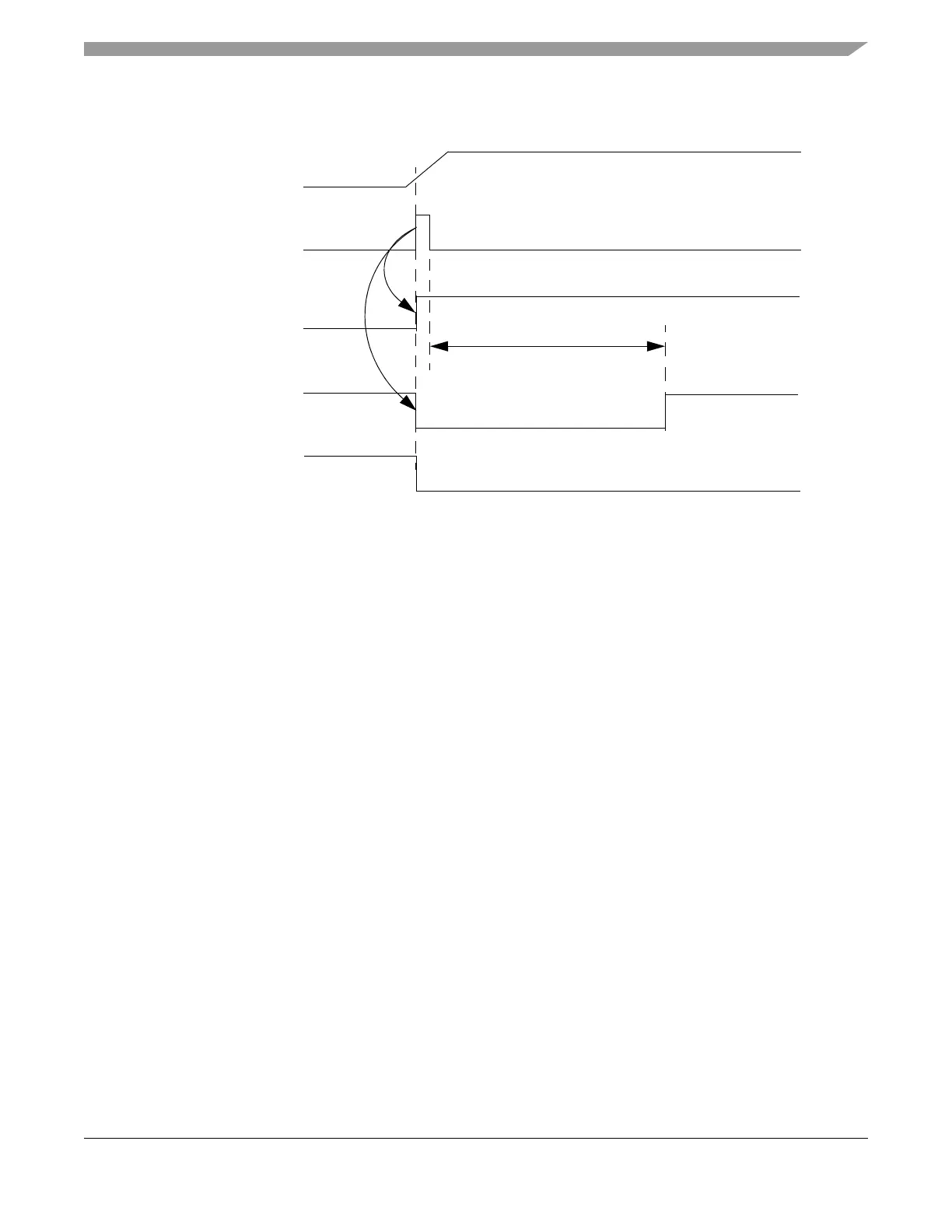

6.4.1.2 Low Voltage and Clock Monitor Reset

When the low voltage reset or clock monitor failure (if enabled) signal is asserted, the CRG asserts the

system reset signal. The CRG synchronously deasserts the system reset signal approximately 16420

EXTAL/CLK_CC clock periods after the deassertion of the low voltage reset or clock monitor failure

signal.

The CRG resets the DER.CMIE bit to 0, asserts the INT_CC# interrupt line, and sets the low voltage reset

interrupt flag, CRSR.LVIF, on the rising edge of the low voltage reset signal.

The CRG resets the DER.CMIE bit to 0, asserts the INT_CC# interrupt line, and sets the clock monitor

failure interrupt flag, CRSR.CMIF, on the rising edge of the clock monitor failure signal (if this is enabled).

NOTE

The CRG deasserts the INT_CC# signal when the CRSR.PRIF,

CRSR.LVIF, CRSR.CMIF and CRSR.ERIF bits are 0.

Figure 6-4 and Figure 6-5 show the operations performed by the CRG when a low voltage reset or a clock

monitor failure (if enabled) signal occurs.

VDD2_5

power-on reset

system reset

~16420 EXTAL/CLK_CC periods

CRSR.PRIF

INT_CC#

Loading...

Loading...