FlexRay Module (FLEXRAYV4)

MFR4310 Reference Manual, Rev. 2

88 Freescale Semiconductor

3.3.2.15 Message Buffer Interrupt Vector Register (MBIVEC)

This register indicates the lowest numbered receive message buffer and the lowest numbered transmit

message buffer that have their interrupt status flag MBIF and interrupt enable MBIE bits asserted. This

means that message buffers with lower message buffer numbers have higher priority.

3

SPL_EF

Static Payload Length Error Flag — This flag is set if the payload length written into the message buffer header

field of a single or double transmit message buffer assigned to the static segment is different from the payload

length for the static segment as it is configured in the corresponding protocol configuration register field

payload_length_static in the Protocol Configuration Register 19 (PCR19).

0 No such error occurred

1 Static payload length error occurred

2

NML_EF

Network Management Length Error Flag — This flag is set if the payload length written into the header

structure of a receive message buffer assigned to the static segment is less than the configured length of the

Network Management Vector as configured in the Network Management Vector Length Register (NMVLR). In

this case, the received part of the Network Management Vector is used to update the Network Management

Vector.

0 No such error occurred

1 Network management length error occurred

1

NMF_EF

Network Management Frame Error Flag — This flag is set if a received message in the static segment with a

Preamble Indicator flag PP asserted has its Null Frame indicator flag NF asserted as well. In this case, the Global

Network Management Registers (see Network Management Vector Registers (NMVR0–NMVR5)) are not

updated.

0 No such error occurred

1 Network management frame error occurred

0

ILSA_EF

Illegal System Memory Access Error Flag — This flag is set if the external system memory subsystem has

detected and indicated an illegal system memory access from the FlexRay module. The exact meaning of an

illegal system memory access is defined by the current implementation of the memory subsystem.

0 No such event.

1 Illegal system memory access occurred.

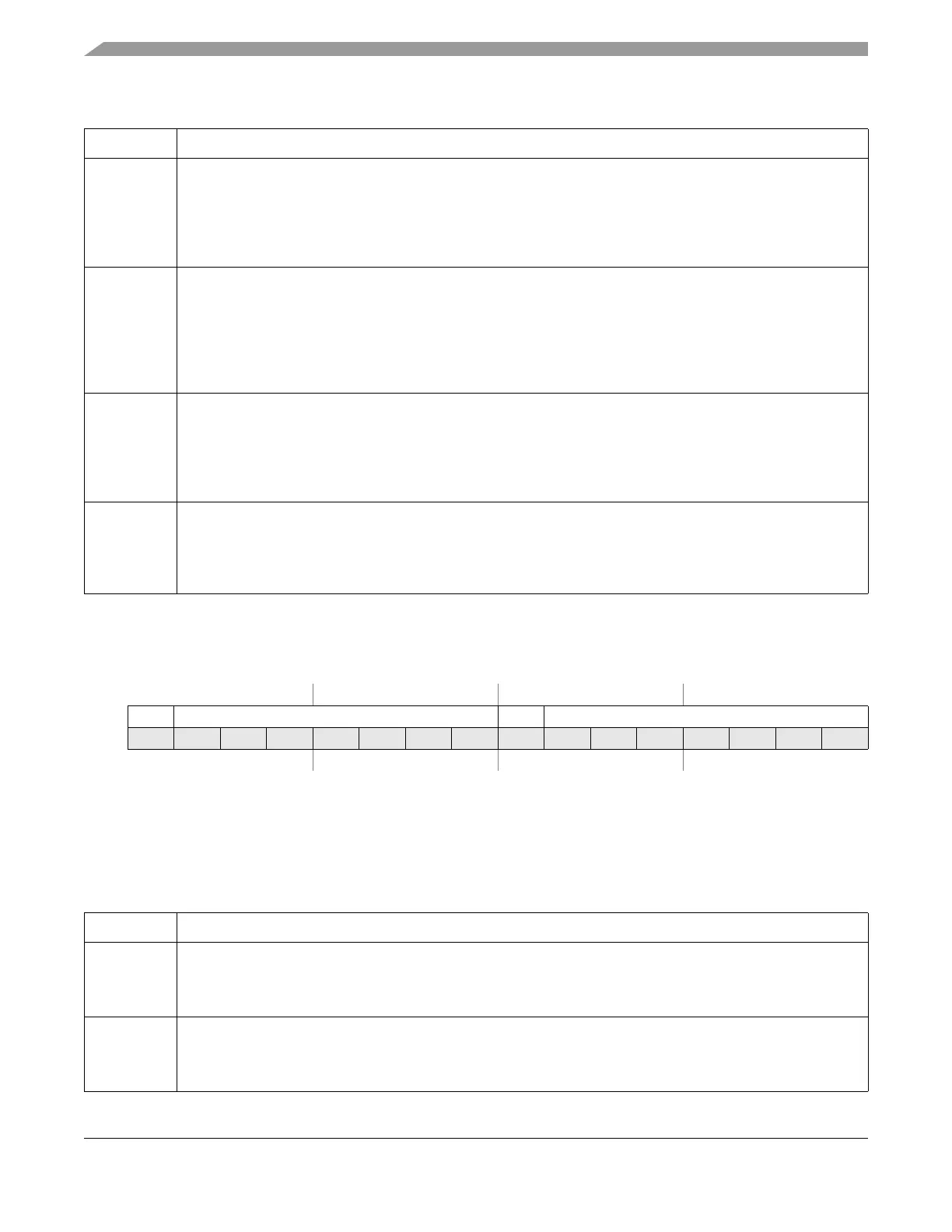

0x0022

1514131211109876543210

R 0 TBIVEC 0 RBIVEC

W

Reset0000000000000000

Figure 3-14. Message Buffer Interrupt Vector Register (MBIVEC)

Table 3-22. MBIVEC Field Descriptions

Field Description

14-8

TBIVEC

Transmit Buffer Interrupt Vector — This field provides the number of the lowest numbered enabled transmit

message buffer that has its interrupt status flag MBIF and its interrupt enable bit MBIE set. If there is no transmit

message buffer with the interrupt status flag MBIF and the interrupt enable MBIE bits asserted, the value in this

field is set to 0.

6-0

RBIVEC

Receive Buffer Interrupt Vector — This field provides the message buffer number of the lowest numbered

receive message buffer which has its interrupt flag MBIF and its interrupt enable bit MBIE asserted. If there is

no receive message buffer with the interrupt status flag MBIF and the interrupt enable MBIE bits asserted, the

value in this field is set to 0.

Table 3-21. CHIERFR Field Descriptions (Continued)

Field Description

Loading...

Loading...