FlexRay Module (FLEXRAYV4)

MFR4310 Reference Manual, Rev. 2

Freescale Semiconductor 69

3.3.2.2 Register Write Access

This section describes the write access restriction terms that apply to all registers.

3.3.2.2.1 Register Write Access Restriction

For each register bit and register field, the write access conditions are specified in the detailed register

description. A description of the write access conditions is given in Table 3-6. If, for a specific register bit

or field, none of the given write access conditions is fulfilled, any write attempt to this register bit or field

is ignored without any notification. The values of the bits or fields are not changed. The condition term [A

or B] indicates that the register or field can be written to if at least one of the conditions is fulfilled.

3.3.2.2.2 Register Write Access Requirements

For some of the registers, a 16-bit wide write access is required to ensure correct operation. This write

access requirement is stated in the detailed register description for each register affected

3.3.2.2.3 Internal Register Access

The following memory mapped registers are used to access multiple internal registers.

• Strobe Signal Control Register (STBSCR)

• Slot Status Selection Register (SSSR)

• Slot Status Counter Condition Register (SSCCR)

• Receive Shadow Buffer Index Register (RSBIR)

Each of these memory mapped registers provides a SEL field and a WMD bit. The SEL field is used to

select the internal register. The WMD bit controls the write mode. If the WMD bit is set to 0 during the

write access, all fields of the internal register are updated. If the WMD bit set to 1, only the SEL field is

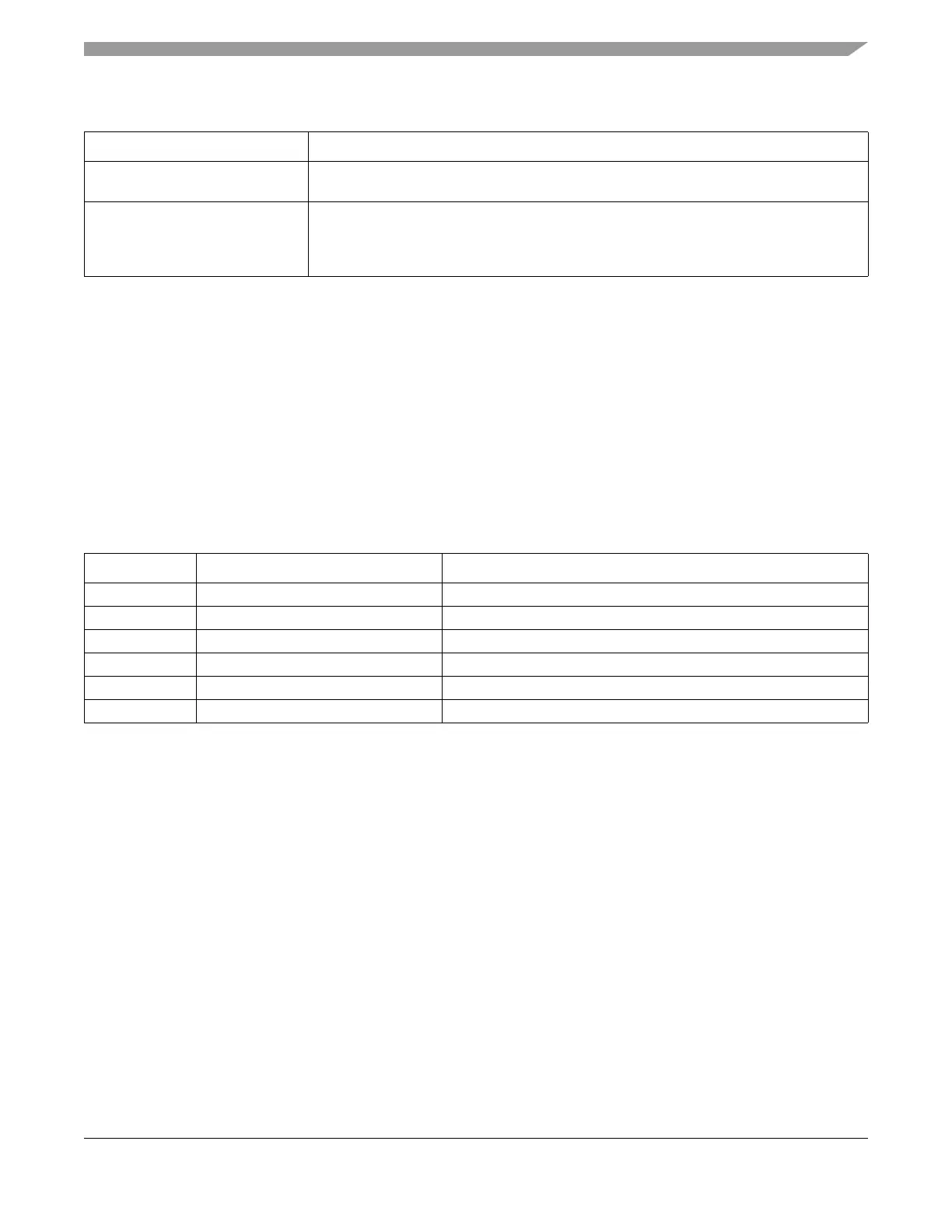

Table 3-5. Additional Register Reset Conditions

Condition Description

Protocol RUN Command The register field is reset when the application writes to RUN command “0101” to the

POCCMD field in the Protocol Operation Control Register (POCR).

Message Buffer Disable The register field is reset when the application has disabled the message buffer.

This happens when the application writes 1 to the message buffer disable trigger bit

MBCCSRn.EDT while the message buffer is enabled (MBCCSn.EDS = 1) and the FlexRay

module grants the disable to the application by clearing the MBCCSRn.EDS bit.

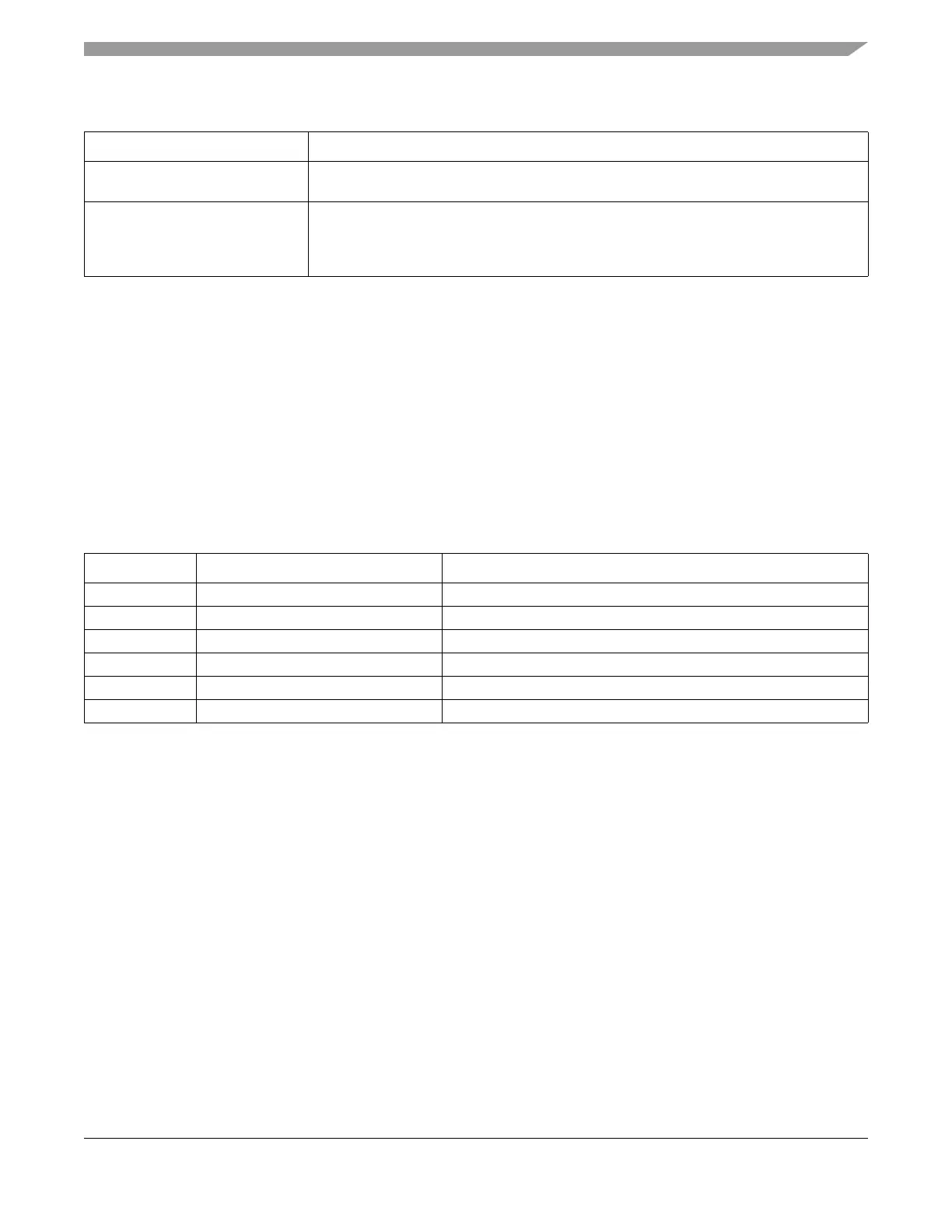

Table 3-6. Register Write Access Restrictions

Condition Indication Description

Any Time - No write access restriction.

Disabled Mode MCR.MEN = 0 Write access only when the FlexRay module is in Disabled Mode.

Normal Mode MCR.MEN = 1 Write access only when the FlexRay module is in Normal Mode.

POC:config PSR0.PROTSTATE = POC:config Write access only when the Protocol is in the POC:config state.

MB_DIS MBCCSRn.EDS = 0 Write access only when the related Message Buffer is disabled.

MB_LCK MBCCSRn.LCKS = 1 Write access only when the related Message Buffer is locked.

Loading...

Loading...