FlexRay Module (FLEXRAYV4)

MFR4310 Reference Manual, Rev. 2

128 Freescale Semiconductor

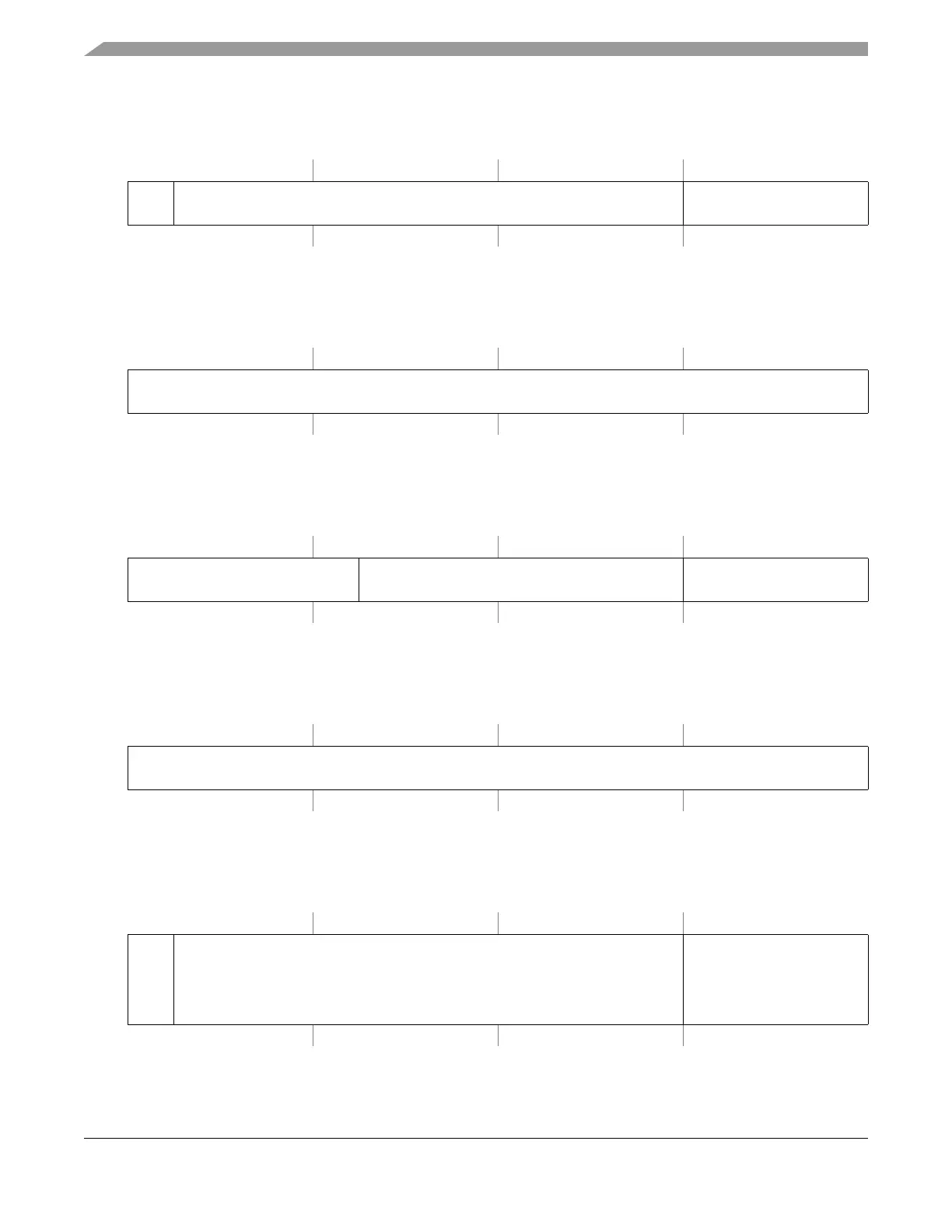

3.3.2.62.23 Protocol Configuration Register 22 (PCR22)

3.3.2.62.24 Protocol Configuration Register 23 (PCR23)

3.3.2.62.25 Protocol Configuration Register 24 (PCR24)

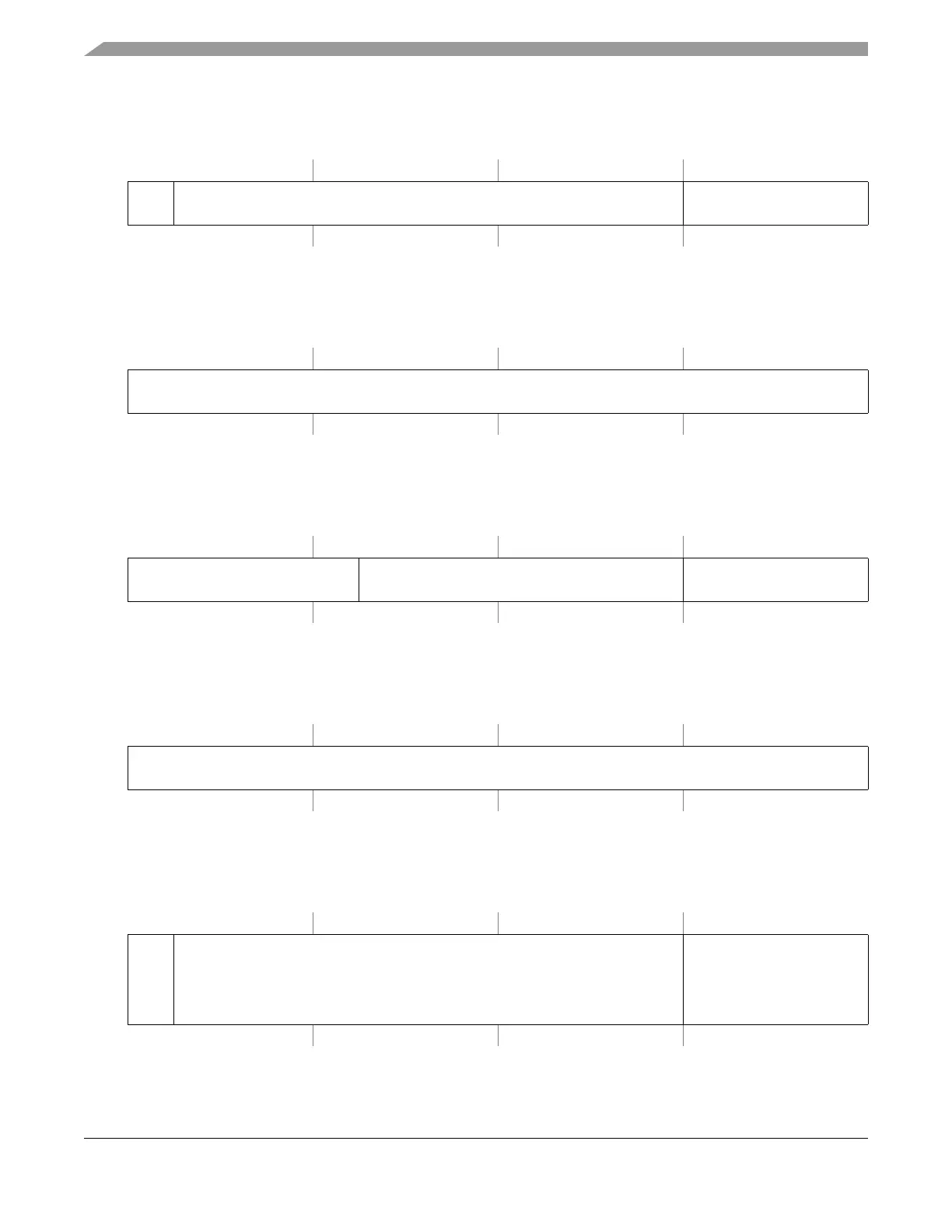

3.3.2.62.26 Protocol Configuration Register 25 (PCR25)

3.3.2.62.27 Protocol Configuration Register 26 (PCR26)

0x00CC Write: POC:config

1514131211109876543210

R

R* comp_accepted_startup_range_a micro_per_cycle[19:16

W

Reset0000000000000000

Figure 3-83. Protocol Configuration Register 22 (PCR22)

0x00CE Write: POC:config

1514131211109876543210

R

micro_per_cycle[15:0]

W

Reset0000000000000000

Figure 3-84. Protocol Configuration Register 23 (PCR23)

0x00D0 Write: POC:config

1514131211109876543210

R

cluster_drift_damping max_payload_length_dynamic

micro_per_cycle_min

[19:16]

W

Reset0000000000000000

Figure 3-85. Protocol Configuration Register 24 (PCR24)

0x00D2 Write: POC:config

1514131211109876543210

R

micro_per_cycle_min[15:0]

W

Reset0000000000000000

Figure 3-86. Protocol Configuration Register 25 (PCR25)

0x00D4 Write: POC:config

1514131211109876543210

R allow

_halt_

due

_to_

clock

comp_accepted_startup_range_b

micro_per_cycle_max

[19:16]

W

Reset0000000000000000

Figure 3-87. Protocol Configuration Register 26 (PCR26)

Loading...

Loading...