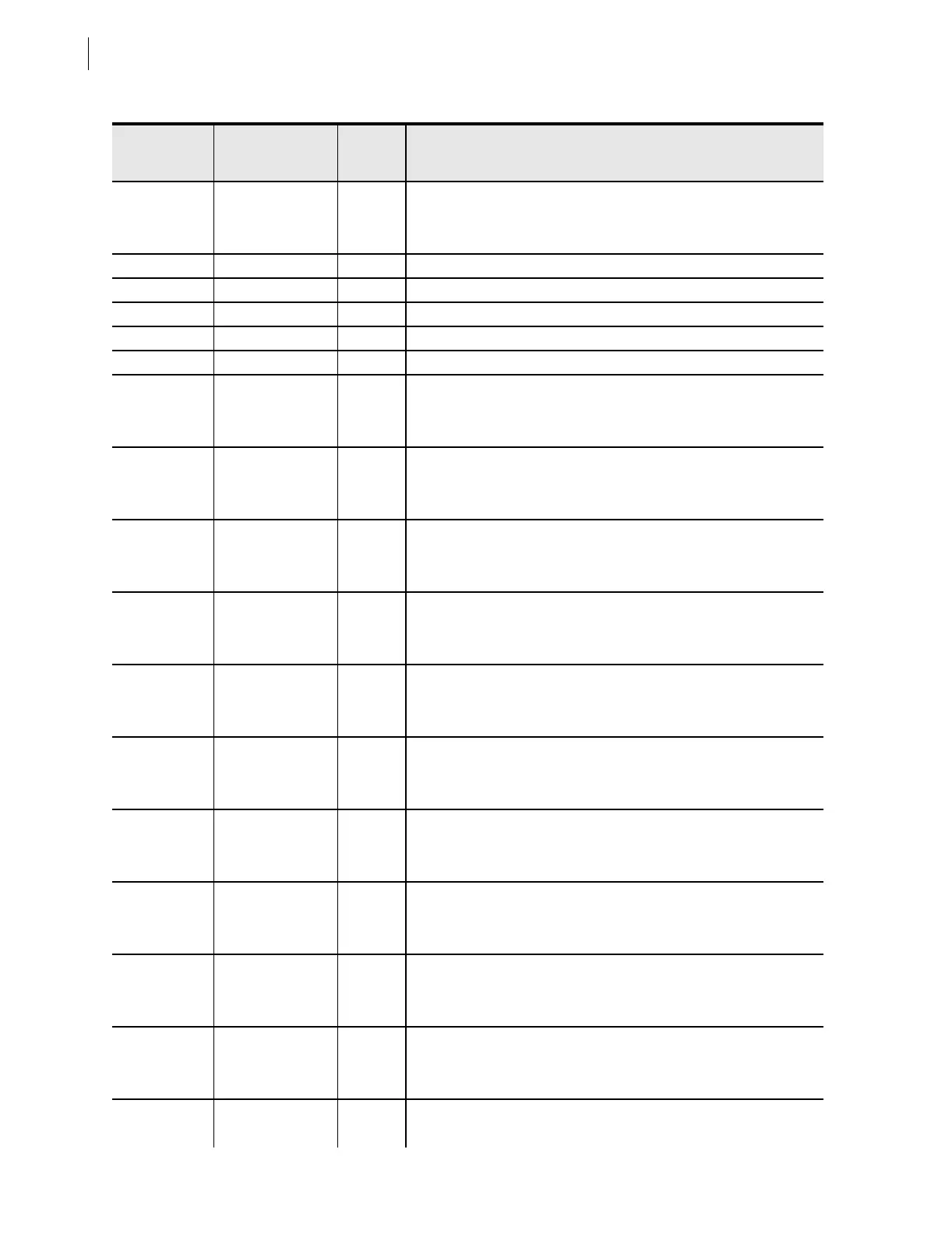

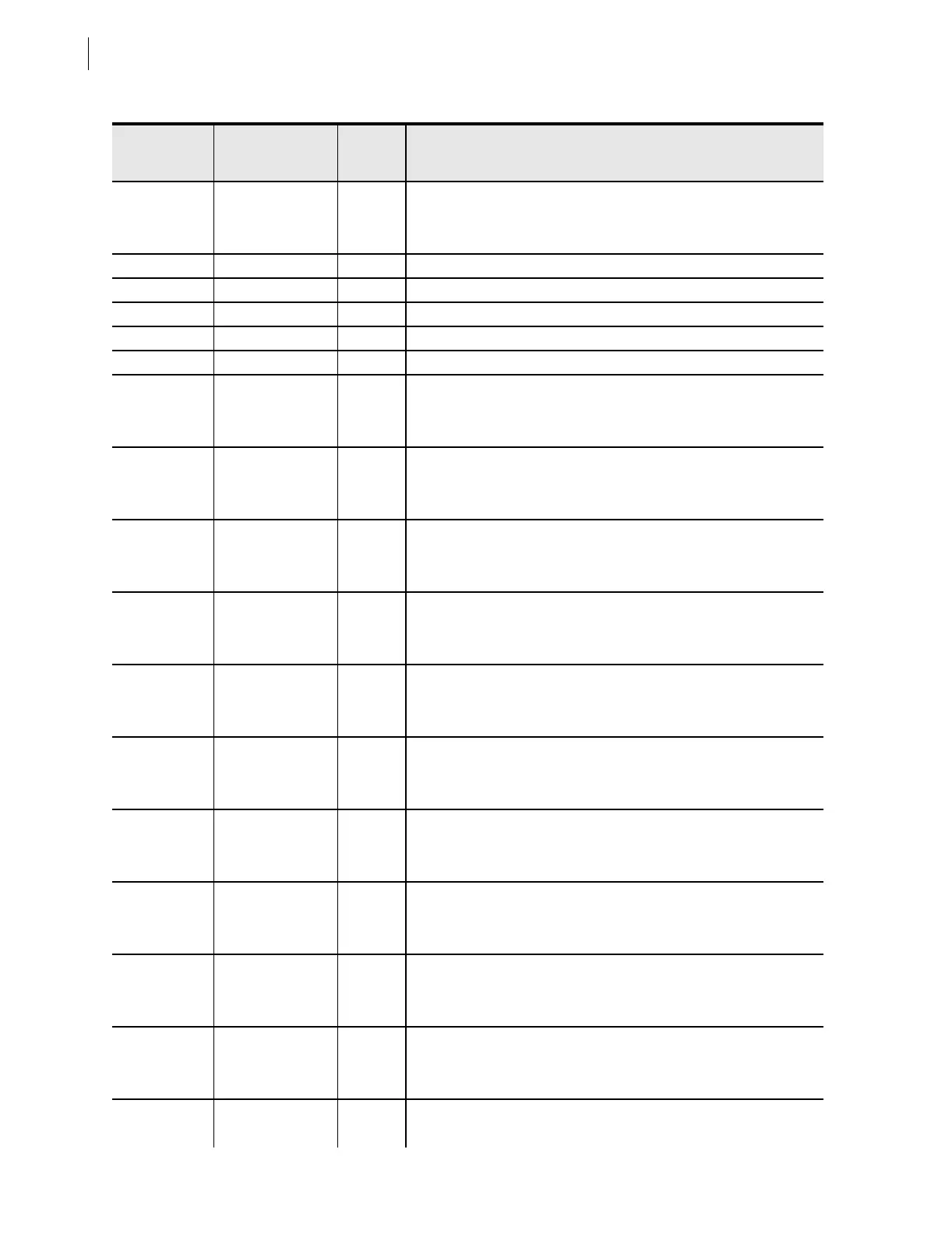

12.16

SEL-311C Relay Instruction Manual Date Code 20060320

Standard Event Reports and SER

Standard 15/30/60/180-Cycle Event Reports

UBB UBB1, UBB2 1 Unblocking block 1 from DCUB logic UBB1 asserted.

2 Unblocking block 2 from DCUB logic UBB2 asserted.

b Both UBB1 and UBB2 asserted.

Z3XT Z3XT * Logic output from Zone/Level 3 extension timer Z3XT asserted.

DSTR DSTRT * Directional carrier start DSTRT asserted.

NSTR NSTRT * Nondirectional carrier start NSTRT asserted.

STOP STOP * Carrier stop STOP asserted.

BTX BTX * Block trip input extension BTX asserted.

TMB A 1 2 TMB1A, TMB2A 1 M

IRRORED BITS channel A transmit bit 1 TMB1A asserted.

2M

IRRORED BITS channel A transmit bit 2 TMB2A asserted.

b Both TMB1A and TMB2A asserted.

TMB A 3 4 TMB3A, TMB4A 3 M

IRRORED BITS channel A transmit bit 3 TMB3A asserted.

4M

IRRORED BITS channel A transmit bit 4 TMB4A asserted.

b Both TMB3A and TMB4A asserted.

TMB A 5 6 TMB5A, TMB6A 5 MIRRORED BITS channel A transmit bit 5 TMB5A asserted.

6M

IRRORED BITS channel A transmit bit 6 TMB6A asserted.

b Both TMB5A and TMB6A asserted.

TMB A 7 8 TMB7A, TMB8A 7 M

IRRORED BITS channel A transmit bit 7 TMB7A asserted.

8M

IRRORED BITS channel A transmit bit 8 TMB8A asserted.

b Both TMB7A and TMB8A asserted.

RMB A 1 2 RMB1A, RMB2A 1 MIRRORED BITS channel A receive bit 1 RMB1A asserted.

2M

IRRORED BITS channel A receive bit 2 RMB2A asserted.

b Both RMB1A and RMB2A asserted.

RMB A 3 4 RMB3A, RMB4A 3 M

IRRORED BITS channel A receive bit 3 RMB3A asserted.

4M

IRRORED BITS channel A receive bit 4 RMB4A asserted.

b Both RMB3A and RMB4A asserted.

RMB A 5 6 RMB5A, RMB6A 5 M

IRRORED BITS channel A receive bit 5 RMB5A asserted.

6M

IRRORED BITS channel A receive bit 6 RMB6A asserted.

b Both RMB5A and RMB6A asserted.

RMB A 7 8 RMB7A, RMB8A 7 M

IRRORED BITS channel A receive bit 7 RMB7A asserted.

8M

IRRORED BITS channel A receive bit 8 RMB8A asserted.

b Both RMB7A and RMB8A asserted.

TMB B 1 2 TMB1B, TMB2B 1 M

IRRORED BITS channel B transmit bit 1 TMB1B asserted.

2M

IRRORED BITS channel B transmit bit 2 bit TMB2B asserted.

b Both TMB1B and TMB2B asserted.

TMB B 3 4 TMB3B, TMB4B 3 M

IRRORED BITS channel B transmit bit 3 TMB3B asserted.

4M

IRRORED BITS channel B transmit bit 4 TMB4B asserted.

b Both TMB3B and TMB4B asserted.

TMB B 5 6 TMB5B, TMB6B 5 MIRRORED BITS channel B transmit bit 5 TMB5B asserted.

6M

IRRORED BITS channel B transmit bit 6 TMB6B asserted.

Table 12.5 Communication Elements Event Report Columns (Sheet 2 of 4)

Column

Heading

Corresponding

Elements

(Relay Word Bits)

Symbol Definition

Loading...

Loading...