DocID13902 Rev 15 1018/1128

RM0008 Ethernet (ETH): media access control (MAC) with DMA controller

1064

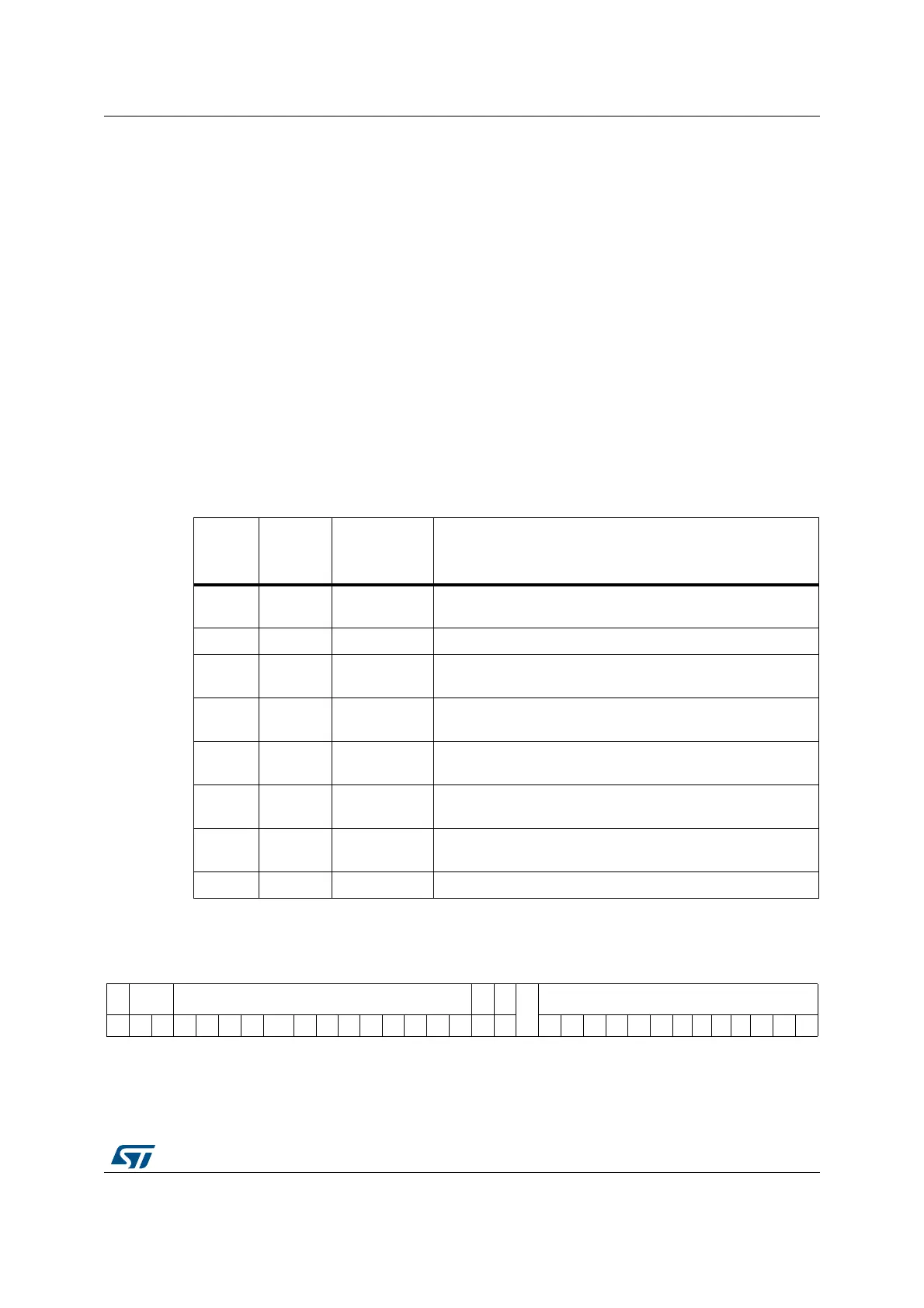

Bits 5, 7, and 0 reflect the conditions discussed in Table 216.

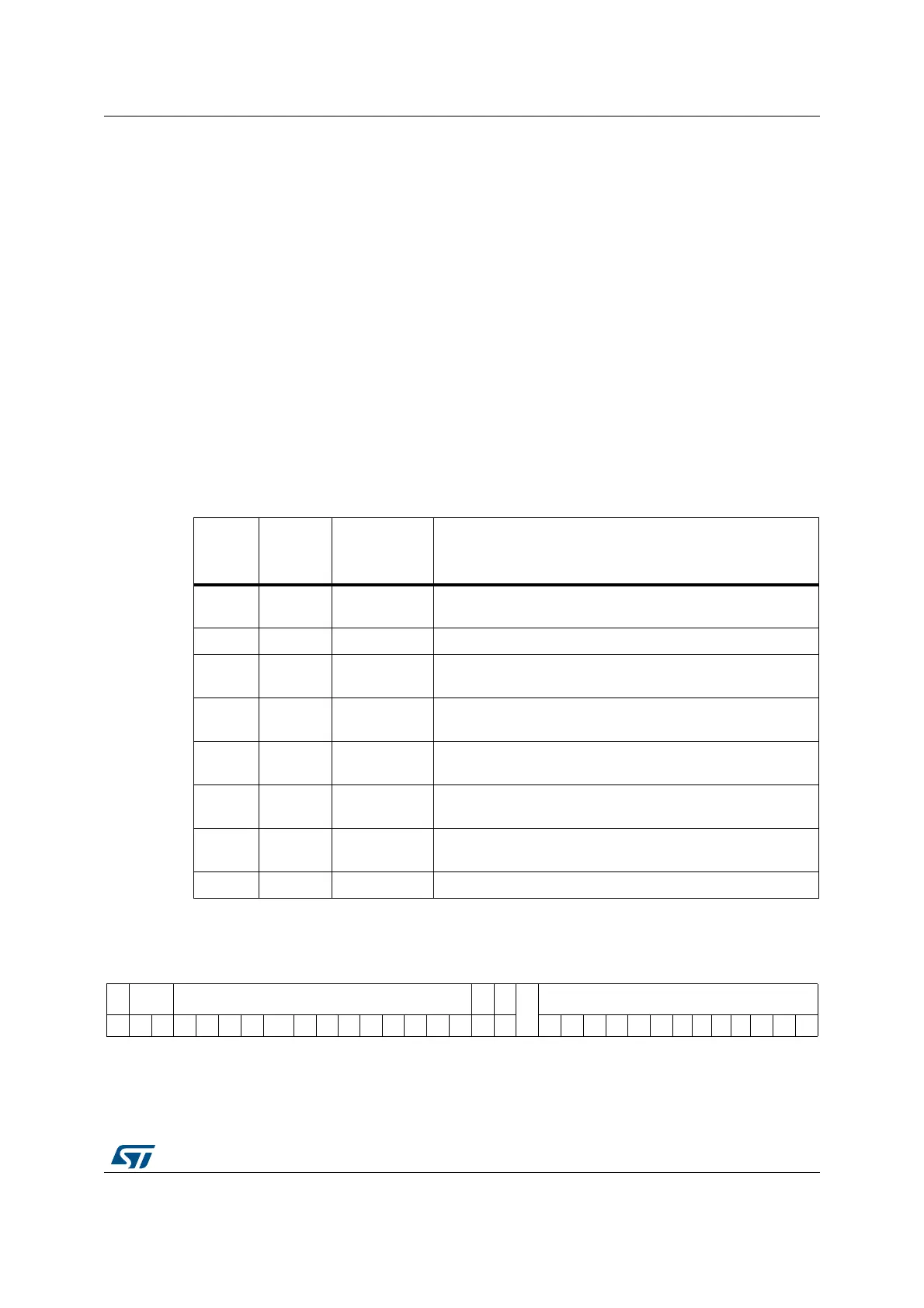

• RDES1: Receive descriptor Word1

Bit 3 RE: Receive error

When set, this bit indicates that the RX_ERR signal is asserted while RX_DV is asserted

during frame reception.

Bit 2 DE: Dribble bit error

When set, this bit indicates that the received frame has a non-integer multiple of bytes (odd

nibbles). This bit is valid only in MII mode.

Bit 1 CE: CRC error

When set, this bit indicates that a cyclic redundancy check (CRC) error occurred on the

received frame. This field is valid only when the last descriptor (RDES0[8]) is set.

Bit 0 PCE: Payload checksum error

When set, it indicates that the TCP, UDP or ICMP checksum the core calculated does not

match the received encapsulated TCP, UDP or ICMP segment’s Checksum field. This bit is

also set when the received number of payload bytes does not match the value indicated in

the Length field of the encapsulated IPv4 or IPv6 datagram in the received Ethernet frame.

Table 216. Receive descriptor 0

Bit 5:

frame

type

Bit 7: IPC

checksum

error

Bit 0: payload

checksum

error

Frame status

00 0

IEEE 802.3 Type frame (Length field value is less than

0x0600.)

1 0 0 IPv4/IPv6 Type frame, no checksum error detected

10 1

IPv4/IPv6 Type frame with a payload checksum error (as described

for PCE) detected

11 0

IPv4/IPv6 Type frame with an IP header checksum error (as

described for IPC CE) detected

11 1

IPv4/IPv6 Type frame with both IP header and payload checksum

errors detected

00 1

IPv4/IPv6 Type frame with no IP header checksum error and the

payload check bypassed, due to an unsupported payload

01 1

A Type frame that is neither IPv4 or IPv6 (the checksum offload

engine bypasses checksum completely.)

0 1 0 Reserved

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DIC

RBS2 RBS2

RER

RCH

Reserved

RBS

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...