Power control (PWR) RM0008

79/1128 DocID13902 Rev 15

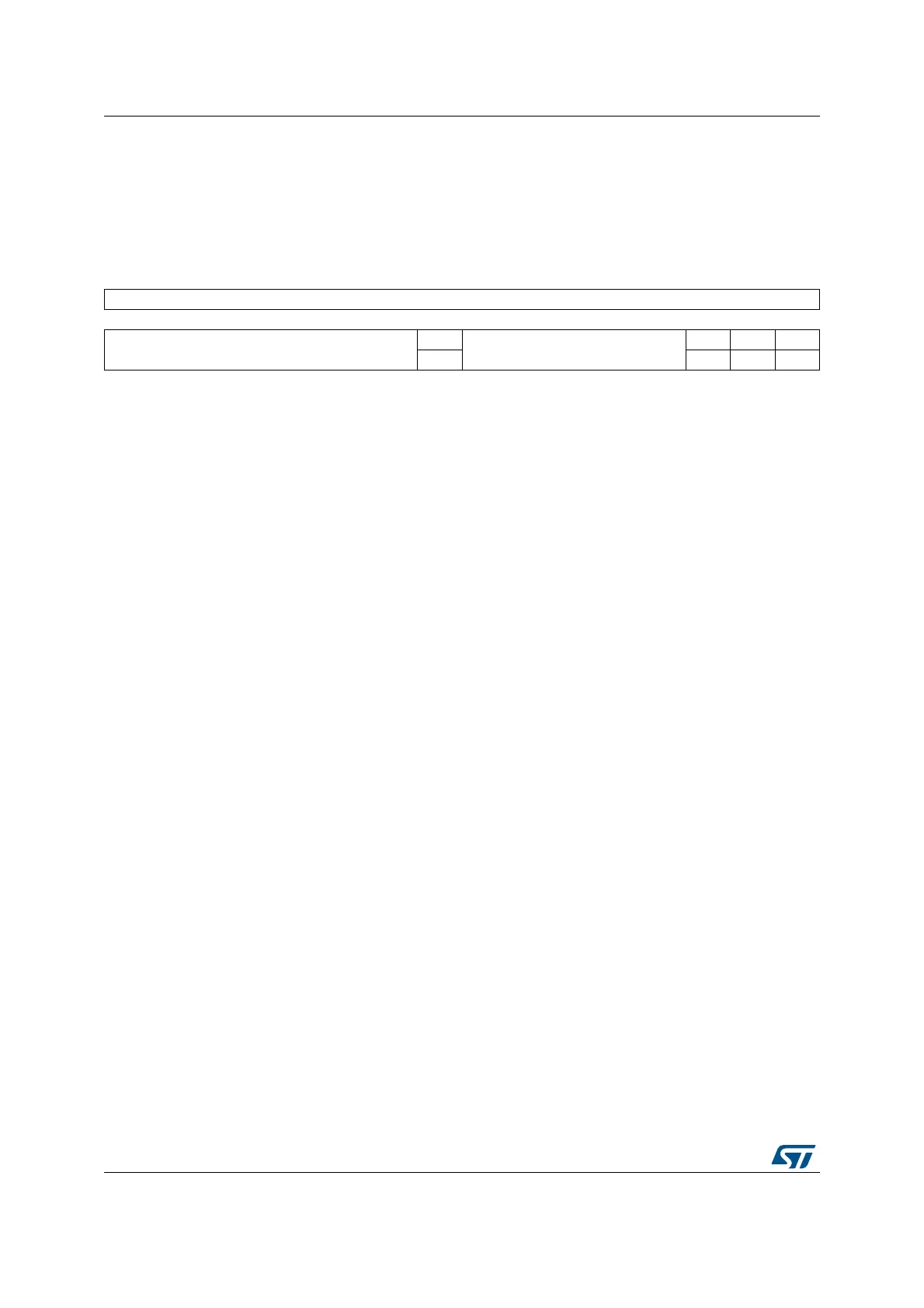

5.4.2 Power control/status register (PWR_CSR)

Address offset: 0x04

Reset value: 0x0000 0000 (not reset by wakeup from Standby mode)

Additional APB cycles are needed to read this register versus a standard APB read.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Reserved

EWUP

Reserved

PVDO SBF WUF

rw r r r

Bits 31:9 Reserved, must be kept at reset value.

Bit 8 EWUP: Enable WKUP pin

This bit is set and cleared by software.

0: WKUP pin is used for general purpose I/O. An event on the WKUP pin does not wakeup

the device from Standby mode.

1: WKUP pin is used for wakeup from Standby mode and forced in input pull down

configuration (rising edge on WKUP pin wakes-up the system from Standby mode).

Note: This bit is reset by a system Reset.

Bits 7:3 Reserved, must be kept at reset value.

Bit 2 PVDO: PVD output

This bit is set and cleared by hardware. It is valid only if PVD is enabled by the PVDE bit.

0: V

DD

/V

DDA

is higher than the PVD threshold selected with the PLS[2:0] bits.

1: V

DD

/V

DDA

is lower than the PVD threshold selected with the PLS[2:0] bits.

Note: The PVD is stopped by Standby mode. For this reason, this bit is equal to 0 after

Standby or reset until the PVDE bit is set.

Bit 1 SBF: Standby flag

This bit is set by hardware and cleared only by a POR/PDR (power on reset/power down reset)

or by setting the CSBF bit in the Power control register (PWR_CR)

0: Device has not been in Standby mode

1: Device has been in Standby mode

Bit 0 WUF: Wakeup flag

This bit is set by hardware and cleared by hardware, by a system reset or by setting the

CWUF bit in the Power control register (PWR_CR)

0: No wakeup event occurred

1: A wakeup event was received from the WKUP pin or from the RTC alarm

Note: An additional wakeup event is detected if the WKUP pin is enabled (by setting the

EWUP bit) when the WKUP pin level is already high.

Loading...

Loading...