DocID13902 Rev 15 150/1128

RM0008 Connectivity line devices: reset and clock control (RCC)

158

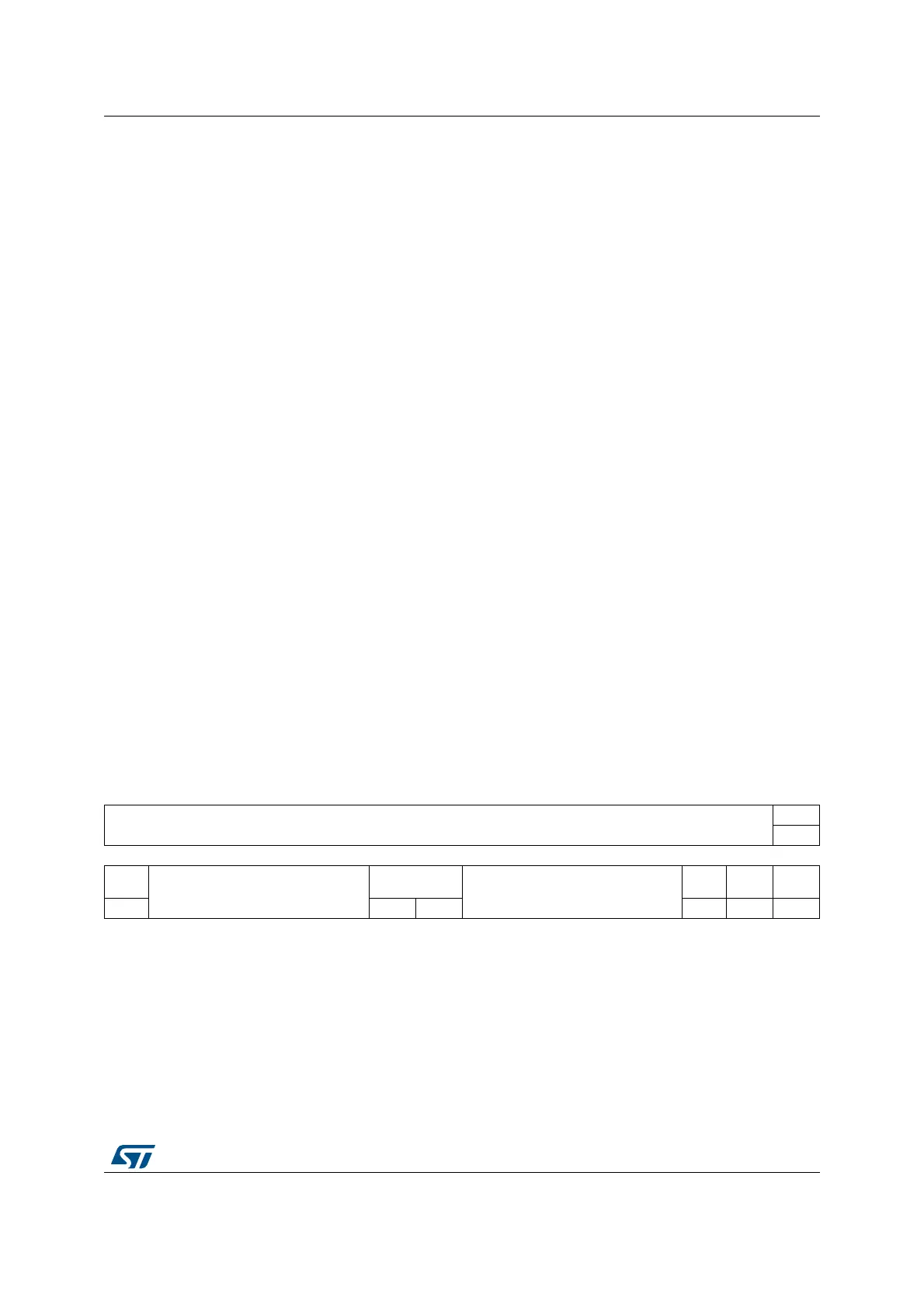

8.3.9 Backup domain control register (RCC_BDCR)

Address: 0x20

Reset value: 0x0000 0000, reset by Backup domain Reset.

Access: 0 ≤ wait state ≤ 3, word, half-word and byte access

Wait states are inserted in the case of successive accesses to this register.

Note: LSEON, LSEBYP, RTCSEL and RTCEN bits of the Backup domain control register

(RCC_BDCR) are in the Backup domain. As a result, after Reset, these bits are write-

protected and the DBP bit in the Power control register (PWR_CR) has to be set before

these can be modified. Refer to Section 6 on page 81 for further information. These bits are

only reset after a Backup domain Reset (see Section 8.1.3: Backup domain reset). Any

internal or external Reset will not have any effect on these bits.

Bit 3 TIM5EN: Timer 5 clock enable

Set and cleared by software.

0: Timer 5 clock disabled

1: Timer 5 clock enabled

Bit 2 TIM4EN: Timer 4 clock enable

Set and cleared by software.

0: Timer 4 clock disabled

1: Timer 4 clock enabled

Bit 1 TIM3EN: Timer 3 clock enable

Set and cleared by software.

0: Timer 3 clock disabled

1: Timer 3 clock enabled

Bit 0 TIM2EN: Timer 2 clock enable

Set and cleared by software.

0: Timer 2 clock disabled

1: Timer 2 clock enabled

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

BDRST

rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RTC

EN

Reserved

RTCSEL[1:0]

Reserved

LSE

BYP

LSE

RDY

LSEON

rw rw rw rw r rw

Loading...

Loading...