Low-, medium-, high- and XL-density reset and clock control (RCC) RM0008

119/1128 DocID13902 Rev 15

7.3.10 Control/status register (RCC_CSR)

Address: 0x24

Reset value: 0x0C00 0000, reset by system Reset, except reset flags by power Reset only.

Access: 0 ≤ wait state ≤ 3, word, half-word and byte access

Wait states are inserted in case of successive accesses to this register.

Bit 2 LSEBYP: External low-speed oscillator bypass

Set and cleared by software to bypass oscillator in debug mode. This bit can be written only

when the external 32 kHz oscillator is disabled.

0: LSE oscillator not bypassed

1: LSE oscillator bypassed

Bit 1 LSERDY: External low-speed oscillator ready

Set and cleared by hardware to indicate when the external 32 kHz oscillator is stable. After

the LSEON bit is cleared, LSERDY goes low after 6 external low-speed oscillator clock

cycles.

0: External 32 kHz oscillator not ready

1: External 32 kHz oscillator ready

Bit 0 LSEON: External low-speed oscillator enable

Set and cleared by software.

0: External 32 kHz oscillator OFF

1: External 32 kHz oscillator ON

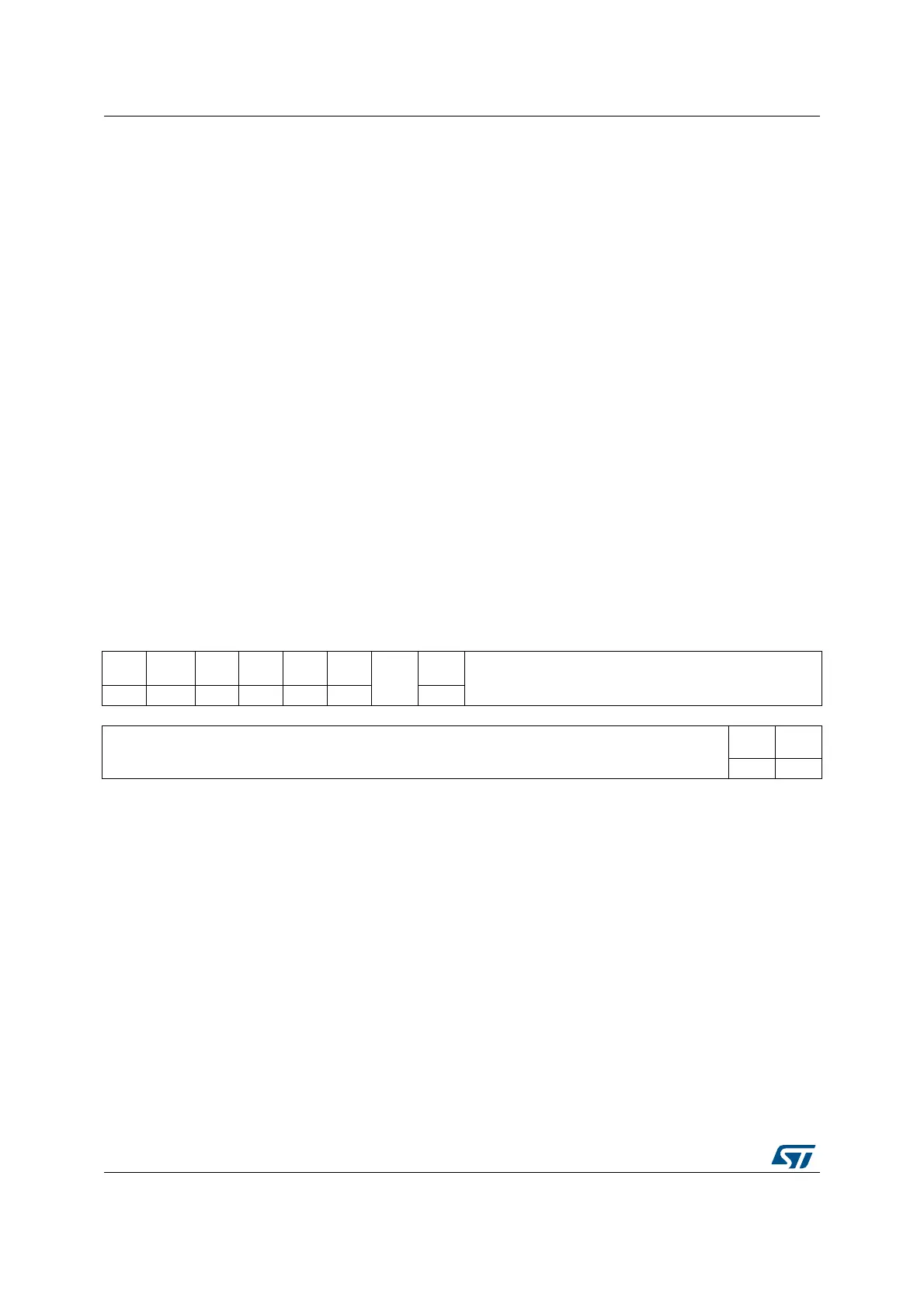

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

LPWR

RSTF

WWDG

RSTF

IWDG

RSTF

SFT

RSTF

POR

RSTF

PIN

RSTF

Res.

RMVF

Reserved

rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

LSI

RDY

LSION

rrw

Loading...

Loading...