Flexible static memory controller (FSMC) RM0008

519/1128 DocID13902 Rev 15

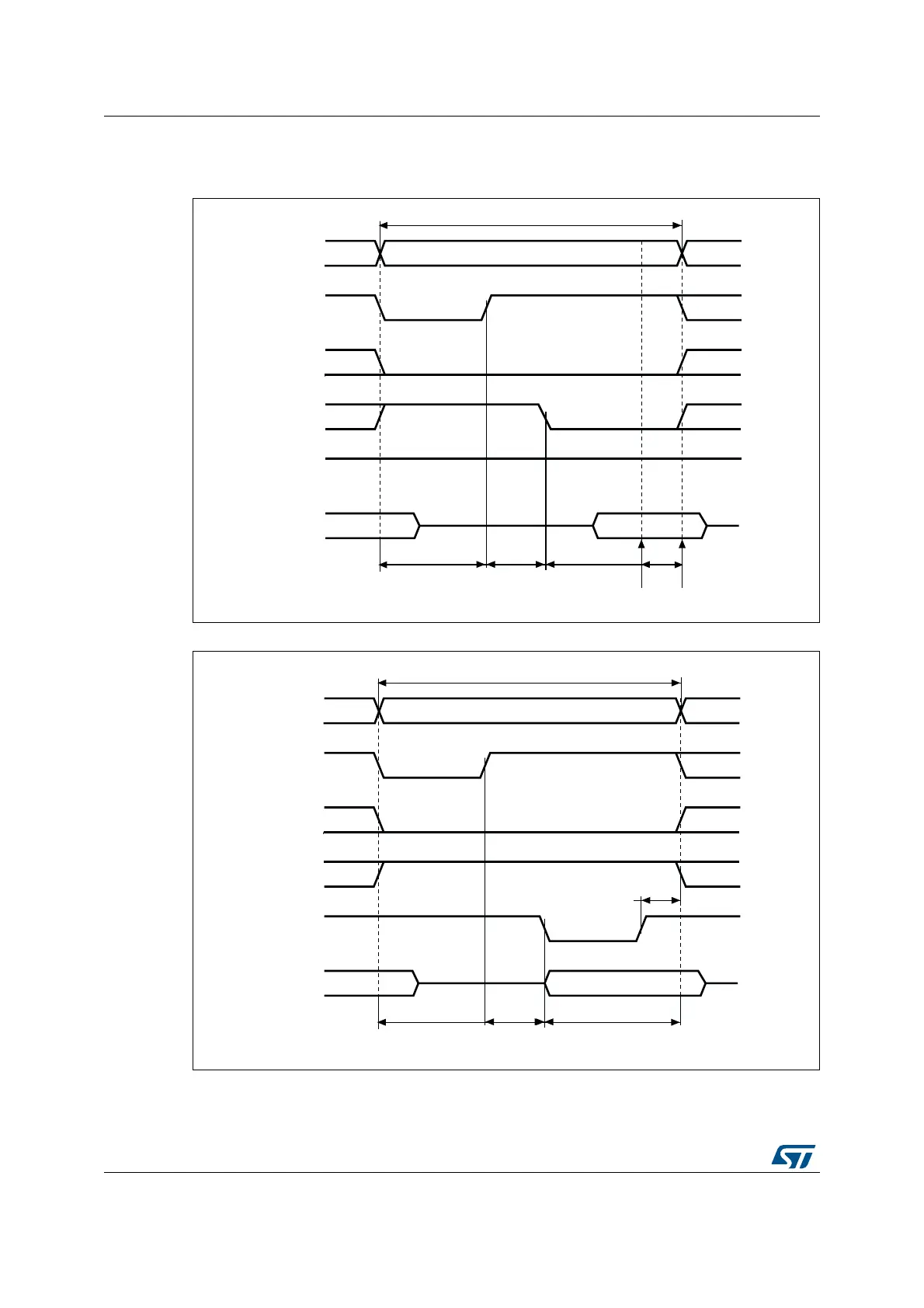

Mode D - asynchronous access with extended address

Figure 196. Mode D read accesses

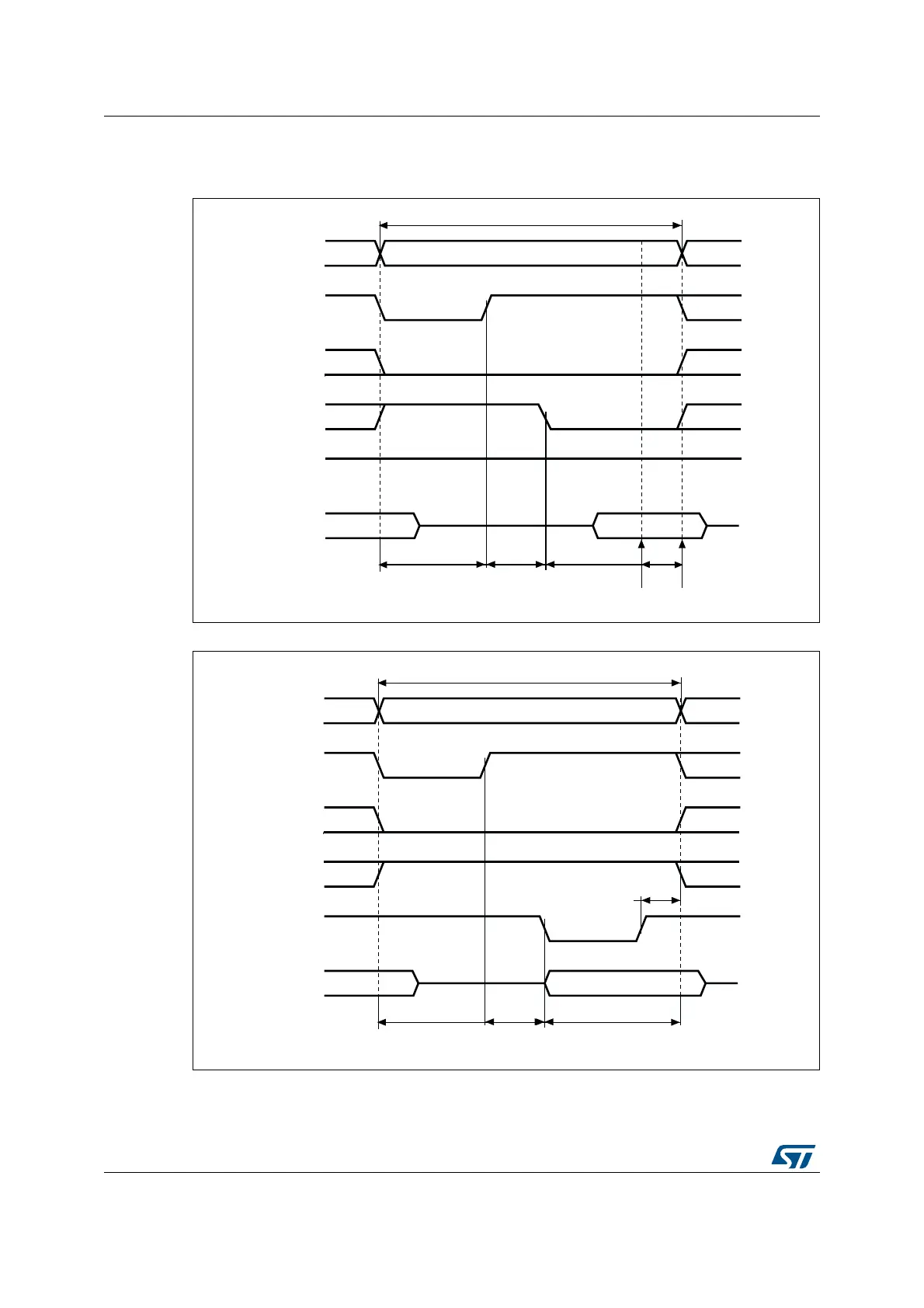

Mode D write accessesThe differences with mode1 are the toggling of NOE that goes on

toggling after NADV changes and the independent read and write timings.

A[25:0]

NOE

(ADDSET +1) (DATAST + 1)

Memory transaction

Data strobe

NEx

D[15:0]

HCLK cycles HCLK cycles

NWE

NADV

data driven

by memory

ai14726c

High

(ADDHLD + 1)

HCLK cycles

2 HCLK

cycles

Data sampled

A[25:0]

NOE

(ADDSET +1) (DATAST + 1)

Memory transaction

NEx

D[15:0]

HCLK cycles HCLK cycles

NWE

NADV

data driven by FSMC

ai14727c

1HCLK

(ADDHLD + 1)

HCLK cycles

Loading...

Loading...