DocID13902 Rev 15 184/1128

RM0008 General-purpose and alternate-function I/Os (GPIOs and AFIOs)

195

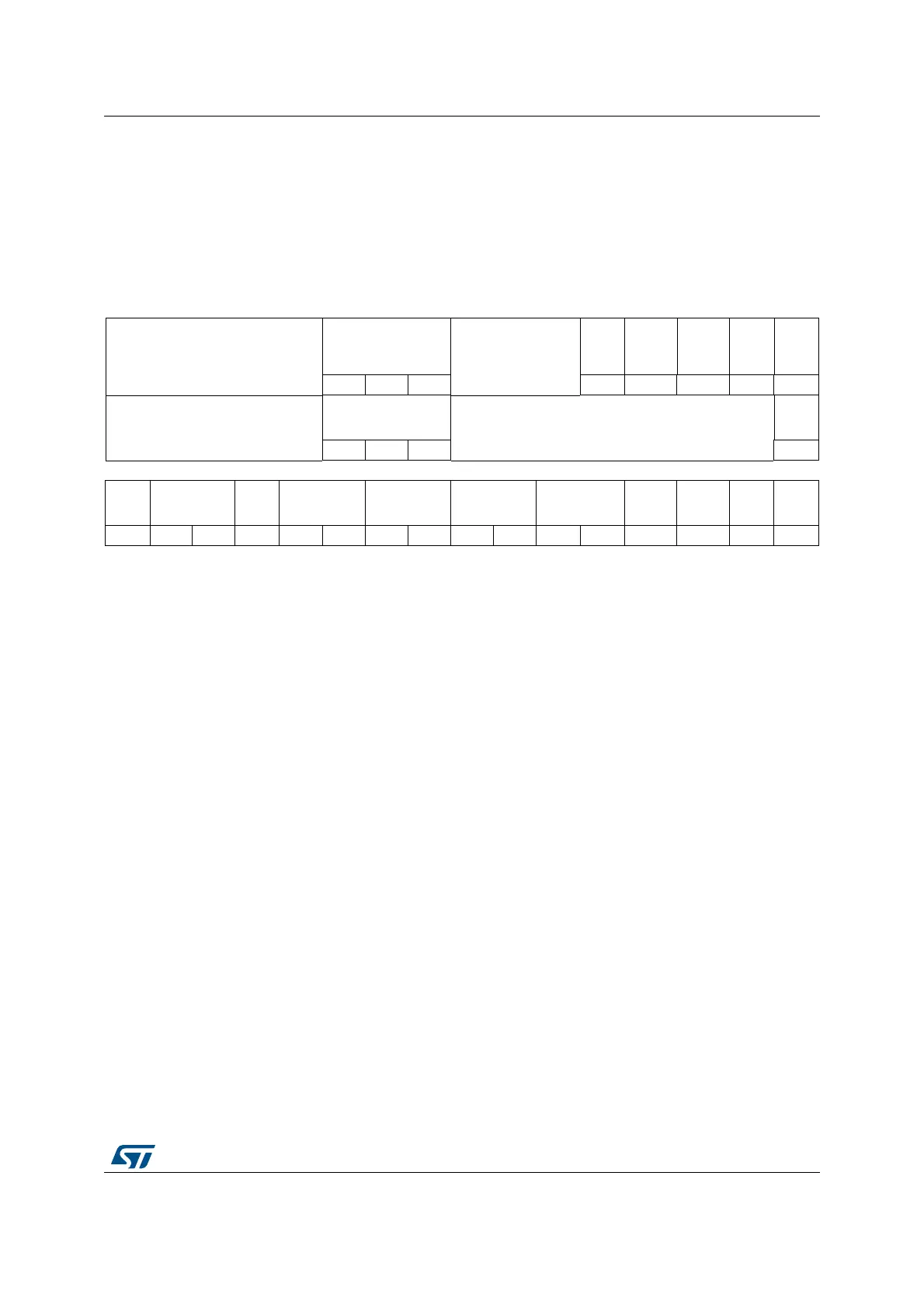

9.4.2 AF remap and debug I/O configuration register (AFIO_MAPR)

Address offset: 0x04

Reset value: 0x0000 0000

Memory map and bit definitions for low-, medium- high- and XL-density

devices:

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

SWJ_

CFG[2:0]

Reserved

ADC2_

ETRG

REG_R

EMAP

ADC2_E

TRGINJ_

REMAP

ADC1_E

TRGRE

G_REMA

P

ADC1_

ETRGI

NJ_RE

MAP

TIM5C

H4_IRE

MAP

www rw rw rw rw rw

Reserved

SWJ_CFG[2:0]

Reserved

TIM5C

H4_IRE

MAP

www rw

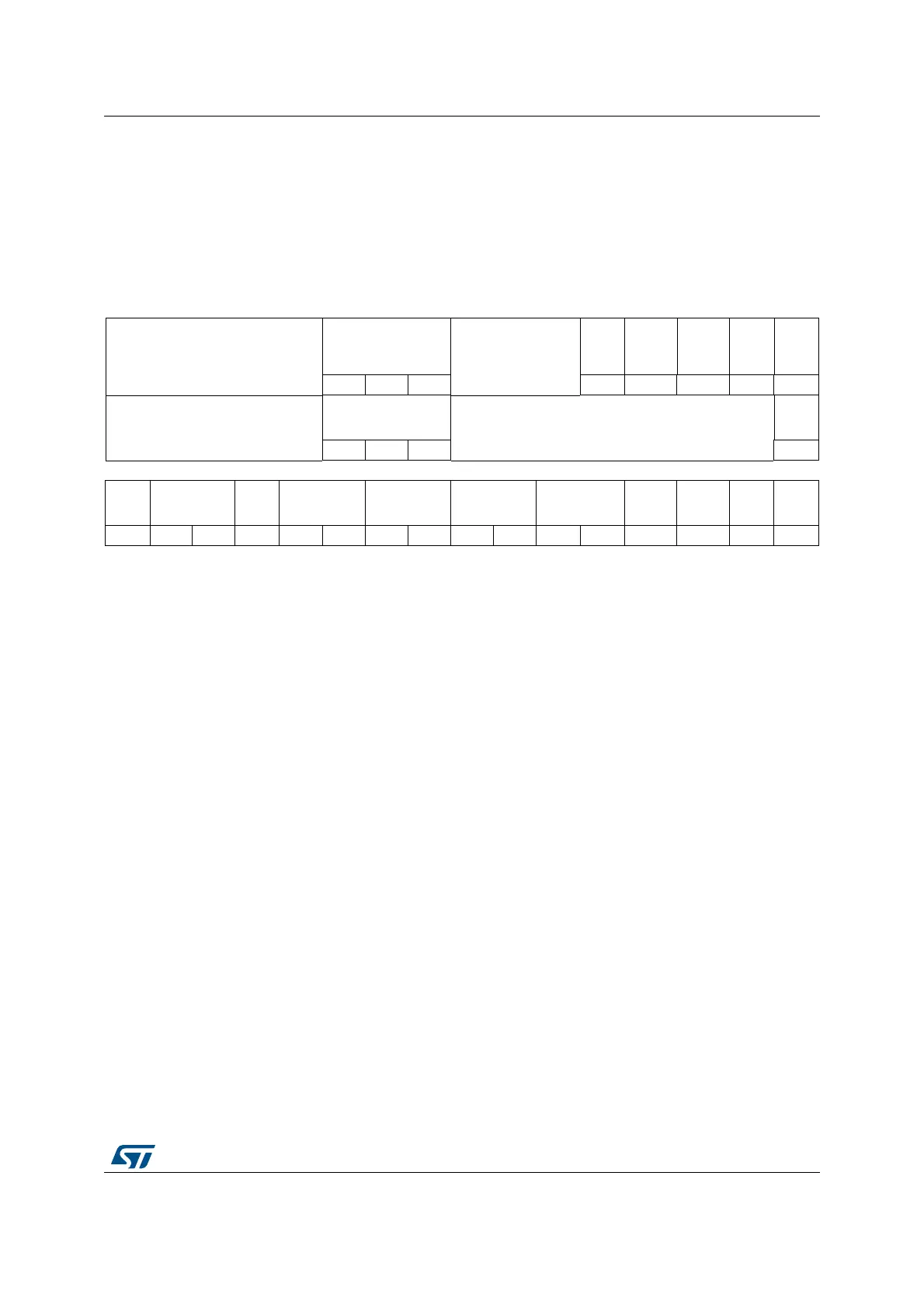

15141312111098765 4 3 2 1 0

PD01_

REMA

P

CAN_REMAP

[1:0]

TIM4_

REMA

P

TIM3_REMAP

[1:0]

TIM2_REMAP

[1:0]

TIM1_REMAP

[1:0]

USART3_

REMAP[1:0]

USART2

_

REMAP

USART1

_

REMAP

I2C1_

REMA

P

SPI1_

REMA

P

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:27 Reserved

Bits 26:24 SWJ_CFG[2:0]: Serial wire JTAG configuration

These bits are write-only (when read, the value is undefined). They are used to configure the

SWJ and trace alternate function I/Os. The SWJ (Serial Wire JTAG) supports JTAG or SWD

access to the Cortex

®

debug port. The default state after reset is SWJ ON without trace.

This allows JTAG or SW mode to be enabled by sending a specific sequence on the JTMS /

JTCK pin.

000: Full SWJ (JTAG-DP + SW-DP): Reset State

001: Full SWJ (JTAG-DP + SW-DP) but without NJTRST

010: JTAG-DP Disabled and SW-DP Enabled

100: JTAG-DP Disabled and SW-DP Disabled

Other combinations: no effect

Bits 23:21 Reserved.

Bits 20 ADC2_ETRGREG_REMAP: ADC 2 external trigger regular conversion remapping

Set and cleared by software. This bit controls the trigger input connected to ADC2 external

trigger regular conversion. When this bit is reset, the ADC2 external trigger regular

conversion is connected to EXTI11. When this bit is set, the ADC2 external event regular

conversion is connected to TIM8_TRGO.

Bits 19 ADC2_ETRGINJ_REMAP: ADC 2 external trigger injected conversion remapping

Set and cleared by software. This bit controls the trigger input connected to ADC2 external

trigger injected conversion. When this bit is reset, the ADC2 external trigger injected

conversion is connected to EXTI15. When this bit is set, the ADC2 external event injected

conversion is connected to TIM8_Channel4.

Bits 18 ADC1_ETRGREG_REMAP: ADC 1 external trigger regular conversion remapping

Set and cleared by software. This bit controls the trigger input connected to ADC1

External trigger regular conversion. When reset the ADC1 External trigger regular

conversion is connected to EXTI11. When set the ADC1 External Event regular conversion

is connected to TIM8 TRGO.

Loading...

Loading...