DocID13902 Rev 15 486/1128

RM0008 Independent watchdog (IWDG)

490

Whenever the key value 0xAAAA is written in the IWDG_KR register, the IWDG_RLR value

is reloaded in the counter and the watchdog reset is prevented.

19.3.1 Hardware watchdog

If the “Hardware watchdog” feature is enabled through the device option bits, the watchdog

is automatically enabled at power-on, and will generate a reset unless the Key register is

written by the software before the counter reaches end of count.

19.3.2 Register access protection

Write access to the IWDG_PR and IWDG_RLR registers is protected. To modify them, you

must first write the code 0x5555 in the IWDG_KR register. A write access to this register

with a different value will break the sequence and register access will be protected again.

This implies that it is the case of the reload operation (writing 0xAAAA).

A status register is available to indicate that an update of the prescaler or the down-counter

reload value is on going.

19.3.3 Debug mode

When the microcontroller enters debug mode (Cortex

®

-M3 core halted), the IWDG counter

either continues to work normally or stops, depending on DBG_IWDG_STOP configuration

bit in DBG module. For more details, refer to Section 31.16.2: Debug support for timers,

watchdog, bxCAN and I2C.

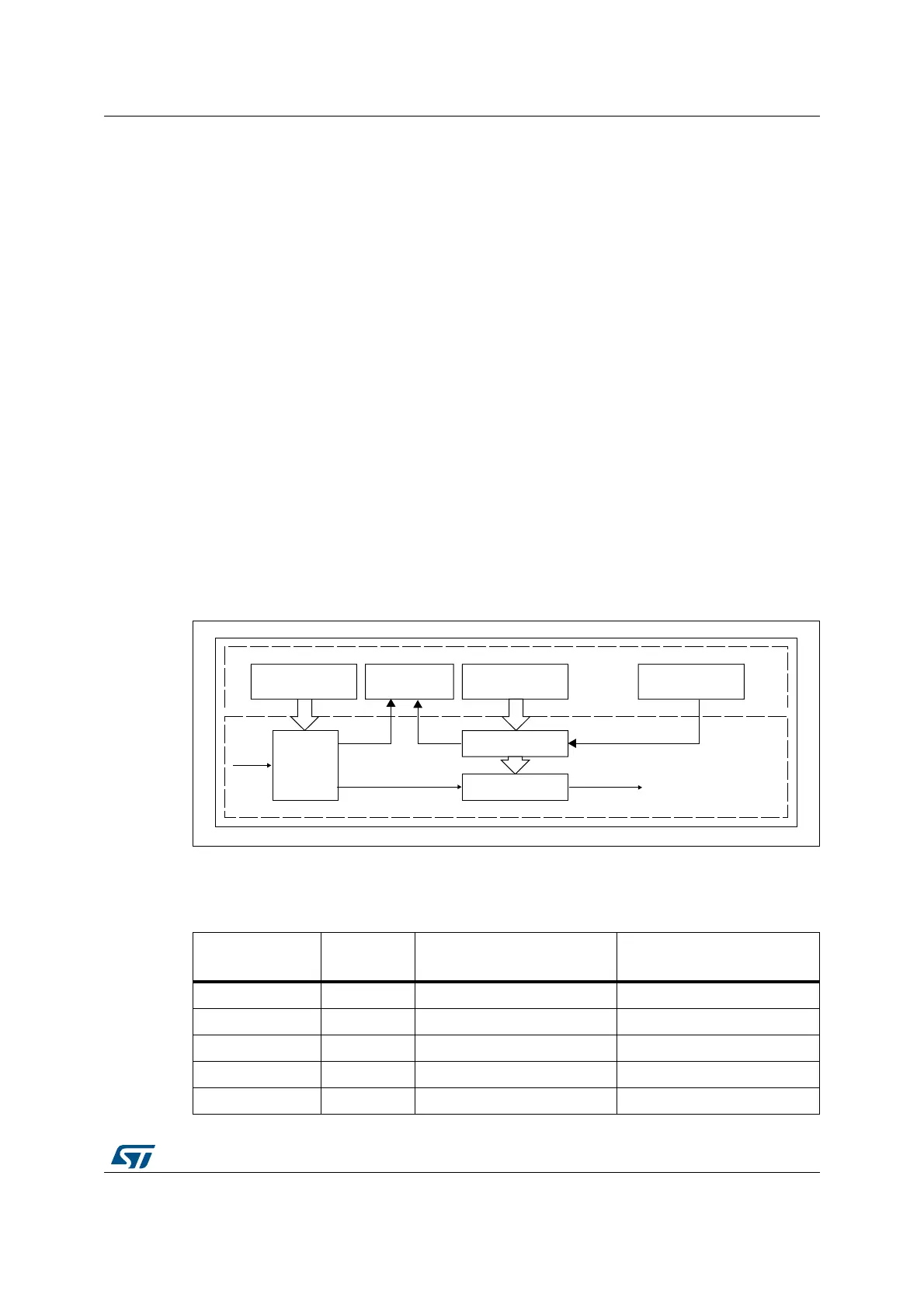

Figure 182. Independent watchdog block diagram

Note: The watchdog function is implemented in the V

DD

voltage domain that is still functional in

Stop and Standby modes.

)7$'RESET

PRESCALER

)7$'?02

0RESCALERREGISTER

)7$'?2,2

2ELOADREGISTER

BIT

,3)

K(Z

)7$'?+2

+EYREGISTER

#/2%

6$$VOLTAGEDOMAIN

)7$'?32

3TATUSREGISTER

-36

BITRELOADVALUE

BITDOWNCOUNTER

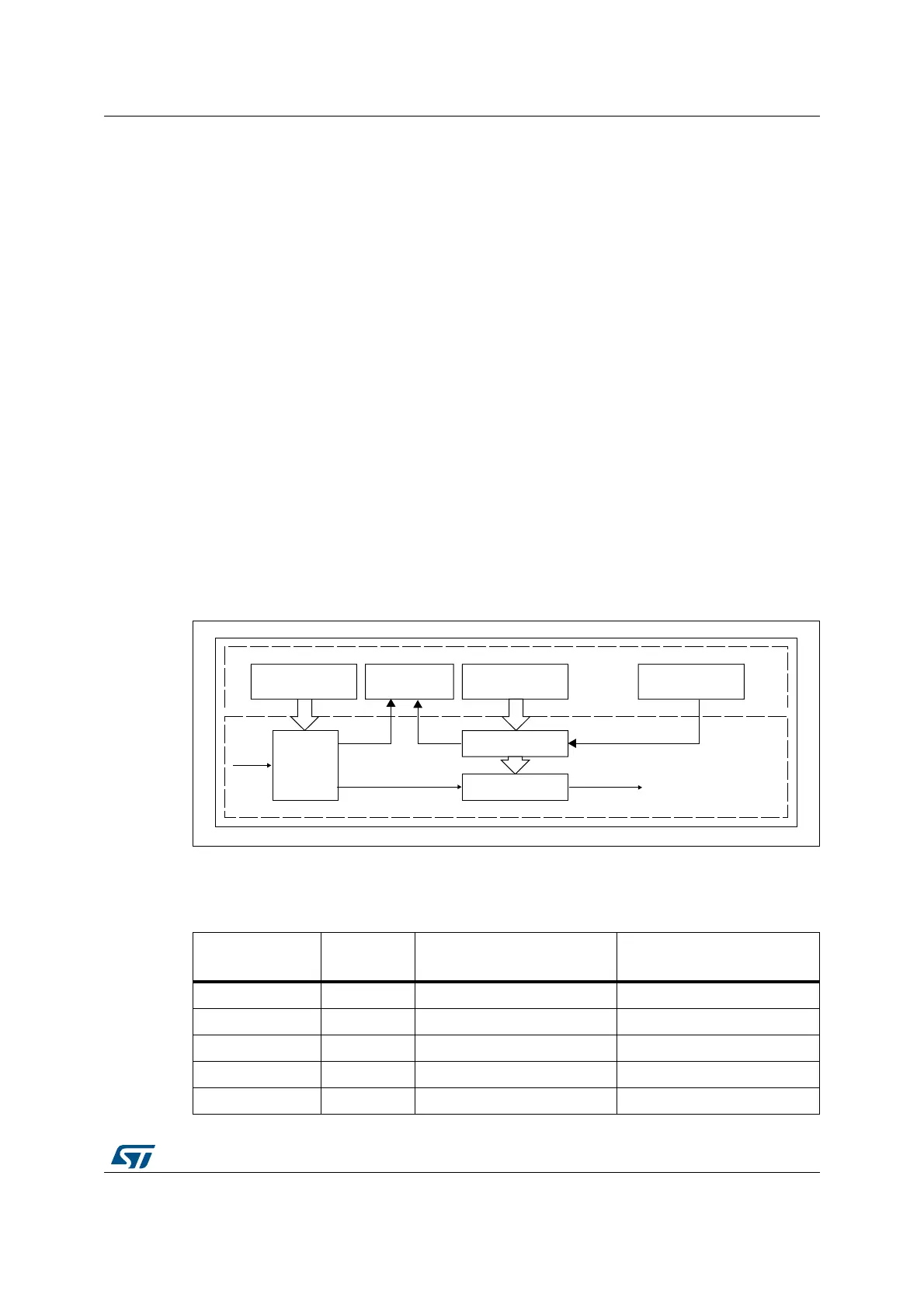

Table 96. Min/max IWDG timeout period at 40 kHz (LSI)

(1)

Prescaler divider PR[2:0] bits

Min timeout (ms) RL[11:0]=

0x000

Max timeout (ms) RL[11:0]=

0xFFF

/4 0 0.1 409.6

/8 1 0.2 819.2

/16 2 0.4 1638.4

/32 3 0.8 3276.8

/64 4 1.6 6553.6

Loading...

Loading...