General-purpose timers (TIM2 to TIM5) RM0008

375/1128 DocID13902 Rev 15

1. As no filter is needed in this example, write ETF[3:0]=0000 in the TIMx_SMCR register.

2. Set the prescaler by writing ETPS[1:0]=01 in the TIMx_SMCR register

3. Select rising edge detection on the ETR pin by writing ETP=0 in the TIMx_SMCR

register

4. Enable external clock mode 2 by writing ECE=1 in the TIMx_SMCR register.

5. Enable the counter by writing CEN=1 in the TIMx_CR1 register.

The counter counts once each 2 ETR rising edges.

The delay between the rising edge on ETR and the actual clock of the counter is due to the

resynchronization circuit on the ETRP signal.

Figure 124. Control circuit in external clock mode 2

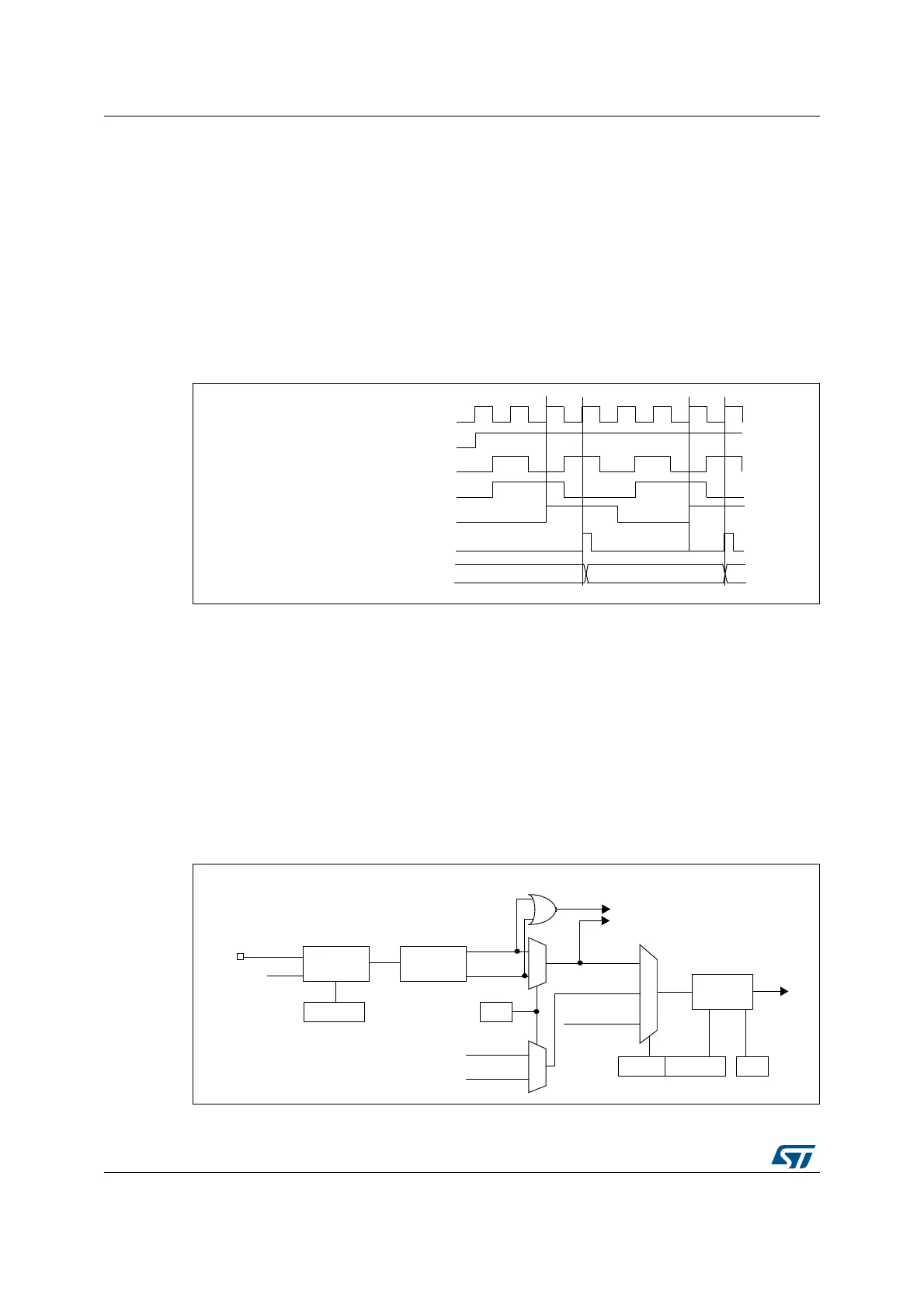

15.3.4 Capture/compare channels

Each Capture/Compare channel is built around a capture/compare register (including a

shadow register), a input stage for capture (with digital filter, multiplexing and prescaler) and

an output stage (with comparator and output control).

The following figure gives an overview of one Capture/Compare channel.

The input stage samples the corresponding TIx input to generate a filtered signal TIxF.

Then, an edge detector with polarity selection generates a signal (TIxFPx) which can be

used as trigger input by the slave mode controller or as the capture command. It is

prescaled before the capture register (ICxPS).

Figure 125. Capture/compare channel (example: channel 1 input stage)

Counter clock = CK_CNT = CK_PSC

Counter register

35 3634

ETR

CNT_EN

CK_INT

ETRP

ETRF

TI1

0

1

TIMx_CCER

CC1P

divider

/1, /2, /4, /8

ICPS[1:0]

TI1F_ED

filter

ICF[3:0]

downcounter

TIMx_CCMR1

Edge

Detector

TI1F_Rising

TI1F_Falling

to the slave mode controller

TI1FP1

11

01

TIMx_CCMR1

CC1S[1:0]

IC1

TI2FP1

TRC

(from channel 2)

(from slave mode

controller)

10

f

DTS

TIMx_CCER

CC1E

IC1PS

TI1F

0

1

TI2F_rising

TI2F_falling

(from channel 2)

Loading...

Loading...