DocID13902 Rev 15 84/1128

RM0008 Backup registers (BKP)

89

6.4.3 Backup control register (BKP_CR)

Address offset: 0x30

Reset value: 0x0000 0000

Note: Setting the TPAL and TPE bits at the same time is always safe, however resetting both at

the same time can generate a spurious Tamper event. For this reason it is recommended to

change the TPAL bit only when the TPE bit is reset.

6.4.4 Backup control/status register (BKP_CSR)

Address offset: 0x34

Reset value: 0x0000 0000

Bit 8 ASOE: Alarm or second output enable

Setting this bit outputs either the RTC Alarm pulse signal or the Second pulse signal on the

TAMPER pin depending on the ASOS bit.

The output pulse duration is one RTC clock period. The TAMPER pin must not be enabled

while the ASOE bit is set.

Note: This bit is reset only by a Backup domain reset.

Bit 7 CCO: Calibration clock output

0: No effect

1: Setting this bit outputs the RTC clock with a frequency divided by 64 on the TAMPER pin.

The TAMPER pin must not be enabled while the CCO bit is set in order to avoid unwanted

Tamper detection.

Note: This bit is reset when the V

DD

supply is powered off.

Bit 6:0 CAL[6:0]: Calibration value

This value indicates the number of clock pulses that will be ignored every 2^20 clock pulses.

This allows the calibration of the RTC, slowing down the clock by steps of 1000000/2^20

PPM.

The clock of the RTC can be slowed down from 0 to 121PPM.

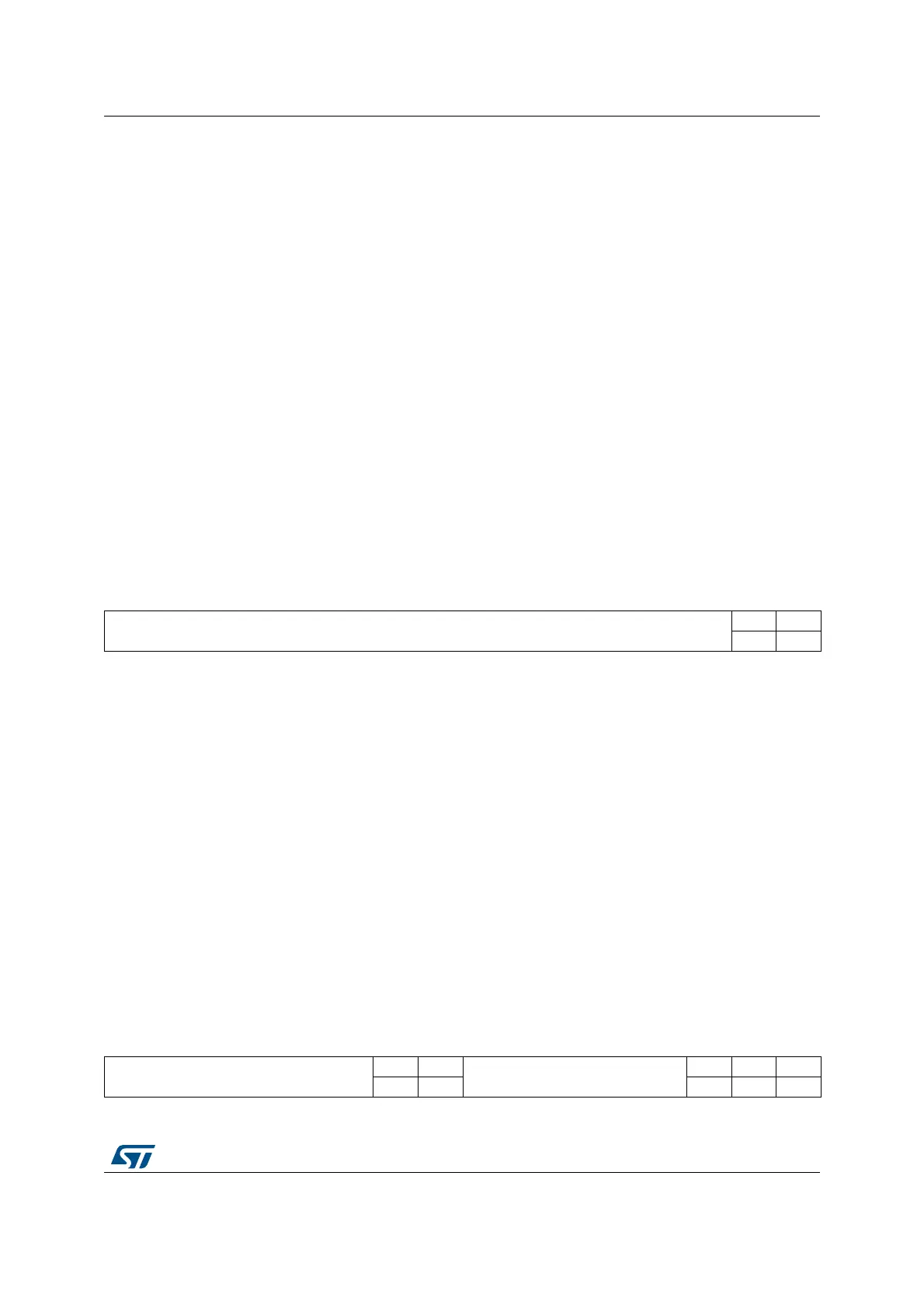

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

TPAL TPE

rw rw

Bits 15:2 Reserved, must be kept at reset value.

Bit 1 TPAL: TAMPER pin active level

0: A high level on the TAMPER pin resets all data backup registers (if TPE bit is set).

1: A low level on the TAMPER pin resets all data backup registers (if TPE bit is set).

Bit 0 TPE: TAMPER pin enable

0: The TAMPER pin is free for general purpose I/O

1: Tamper alternate I/O function is activated.

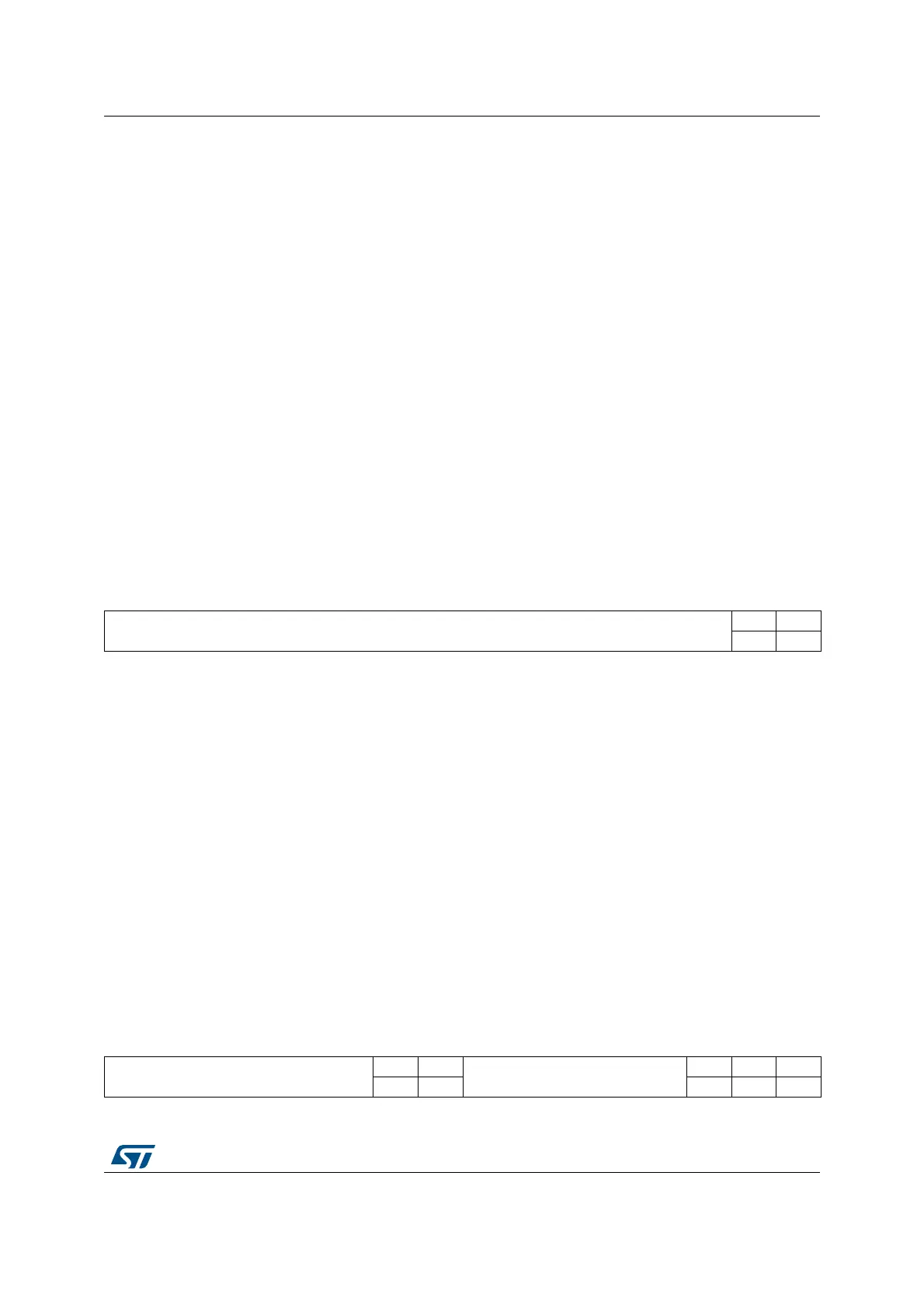

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

TIF TEF

Reserved

TPIE CTI CTE

rr rwww

Loading...

Loading...