DocID13902 Rev 15 792/1128

RM0008 Universal synchronous asynchronous receiver transmitter (USART)

820

Example 2:

To program USARTDIV = 0d25.62

This leads to:

DIV_Fraction = 16*0d0.62 = 0d9.92

The nearest real number is 0d10 = 0xA

DIV_Mantissa = mantissa (0d25.620) = 0d25 = 0x19

Then, USART_BRR = 0x19A hence USARTDIV = 0d25.625

Example 3:

To program USARTDIV = 0d50.99

This leads to:

DIV_Fraction = 16*0d0.99 = 0d15.84

The nearest real number is 0d16 = 0x10 => overflow of DIV_frac[3:0] => carry must be

added up to the mantissa

DIV_Mantissa = mantissa (0d50.990 + carry) = 0d51 = 0x33

Then, USART_BRR = 0x330 hence USARTDIV = 0d51.000

Note: The lower the CPU clock the lower will be the accuracy for a particular Baud rate. The upper

limit of the achievable baud rate can be fixed with this data.

Only USART1 is clocked with PCLK2 (72 MHz Max). Other USARTs are clocked with

PCLK1 (36 MHz Max).

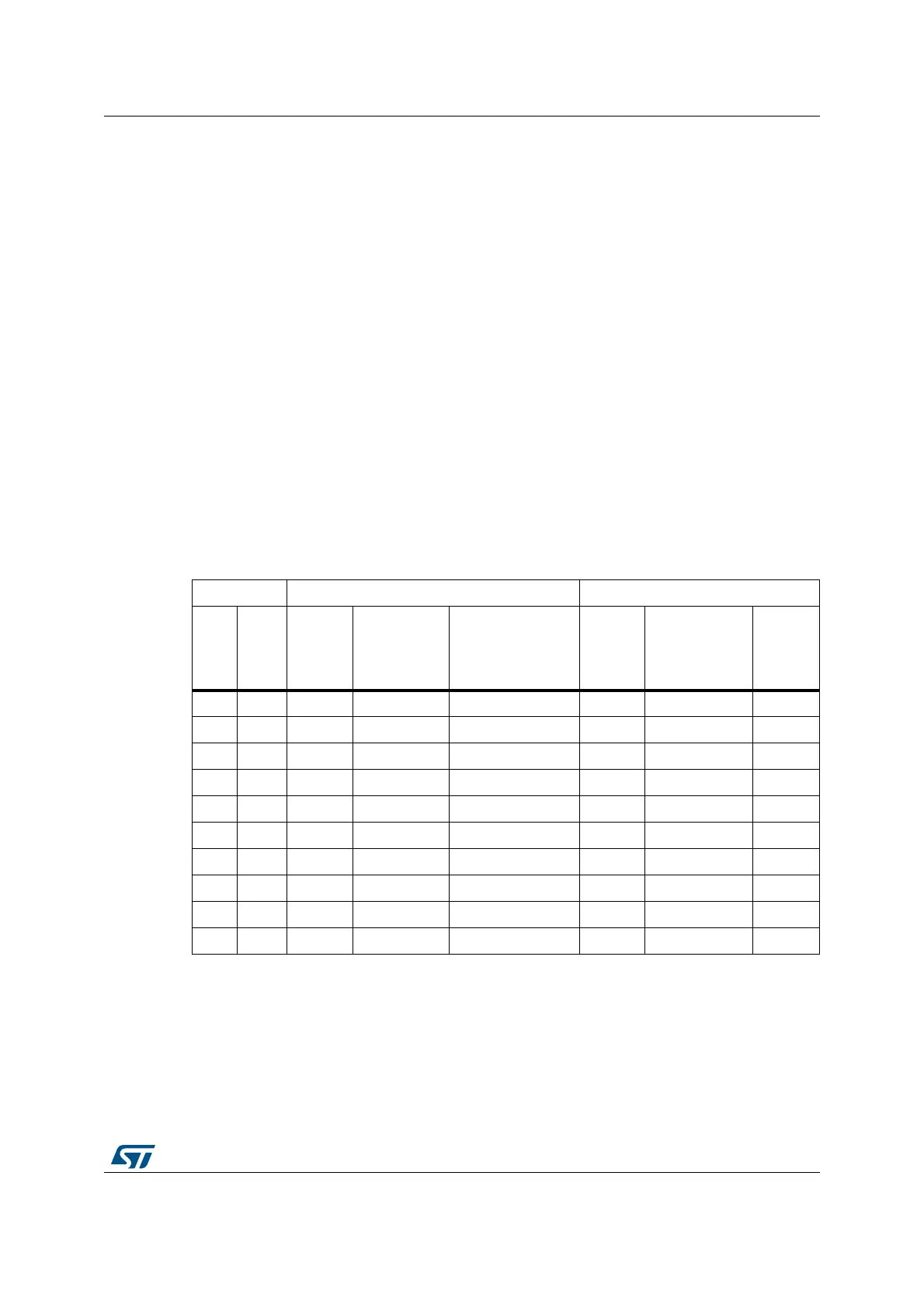

Table 192. Error calculation for programmed baud rates

Baud rate f

PCLK

= 36 MHz f

PCLK

= 72 MHz

S.No

in

Kbps

Actual

Value

programmed

in the Baud

Rate register

% Error

=(Calculated -

Desired)B.Rate

/Desired B.Rate

Actual

Value

programmed

in the Baud

Rate register

% Error

1. 2.4 2.400 937.5 0% 2.4 1875 0%

2. 9.6 9.600 234.375 0% 9.6 468.75 0%

3. 19.2 19.2 117.1875 0% 19.2 234.375 0%

4. 57.6 57.6 39.0625 0% 57.6 78.125 0.%

5. 115.2 115.384 19.5 0.15% 115.2 39.0625 0%

6. 230.4 230.769 9.75 0.16% 230.769 19.5 0.16%

7. 460.8 461.538 4.875 0.16% 461.538 9.75 0.16%

8. 921.6 923.076 2.4375 0.16% 923.076 4.875 0.16%

9. 2250 2250 1 0% 2250 2 0%

10. 4500 NA NA NA 4500 1 0%

Loading...

Loading...