Direct memory access controller (DMA) RM0008

285/1128 DocID13902 Rev 15

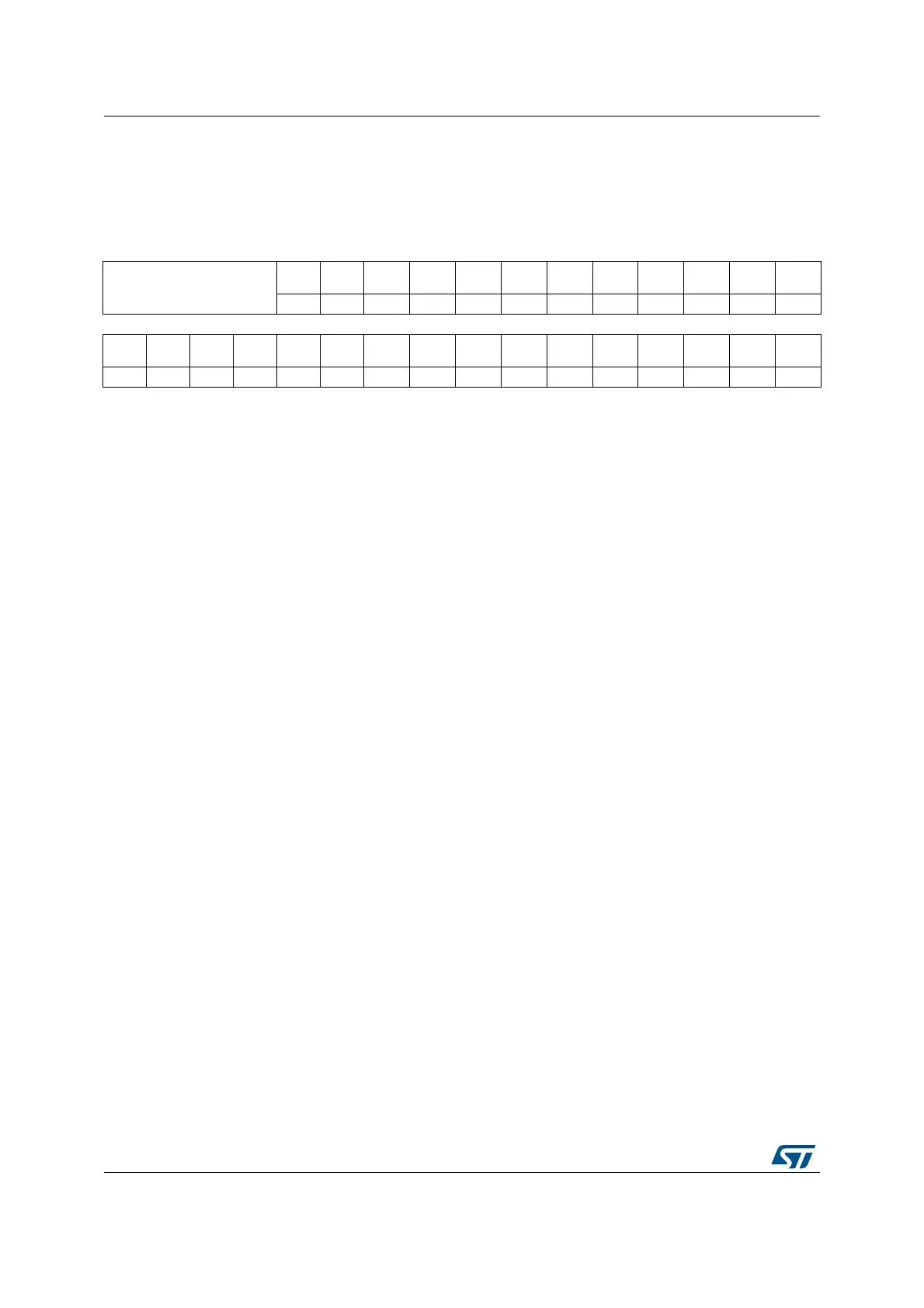

13.4.2 DMA interrupt flag clear register (DMA_IFCR)

Address offset: 0x04

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

CTEIF

7

CHTIF

7

CTCIF7 CGIF7 CTEIF6 CHTIF6 CTCIF6 CGIF6 CTEIF5 CHTIF5 CTCIF5 CGIF5

wwwwwwwwwwww

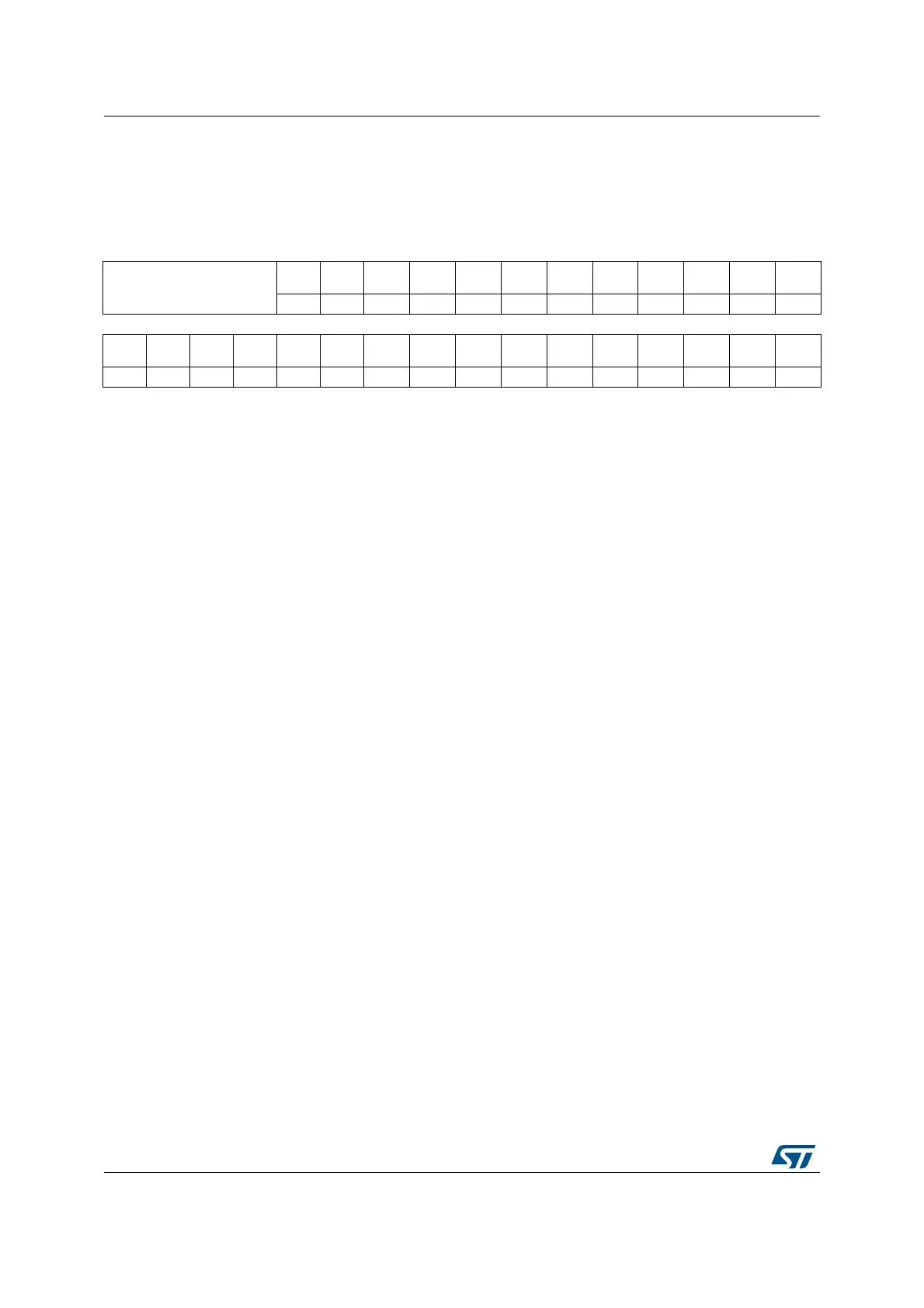

1514131211109876543210

CTEIF

4

CHTIF

4

CTCIF

4

CGIF4

CTEIF

3

CHTIF

3

CTCIF3 CGIF3 CTEIF2 CHTIF2 CTCIF2 CGIF2 CTEIF1 CHTIF1 CTCIF1 CGIF1

wwwwww w w w w w w w w w w

Bits 31:28 Reserved, must be kept at reset value.

Bits 27, 23, 19, 15,

11, 7, 3

CTEIFx: Channel x transfer error clear (x = 1 ..7)

This bit is set and cleared by software.

0: No effect

1: Clears the corresponding TEIF flag in the DMA_ISR register

Bits 26, 22, 18, 14,

10, 6, 2

CHTIFx: Channel x half transfer clear (x = 1 ..7)

This bit is set and cleared by software.

0: No effect

1: Clears the corresponding HTIF flag in the DMA_ISR register

Bits 25, 21, 17, 13,

9, 5, 1

CTCIFx: Channel x transfer complete clear (x = 1 ..7)

This bit is set and cleared by software.

0: No effect

1: Clears the corresponding TCIF flag in the DMA_ISR register

Bits 24, 20, 16, 12,

8, 4, 0

CGIFx: Channel x global interrupt clear (x = 1 ..7)

This bit is set and cleared by software.

0: No effect

1: Clears the GIF, TEIF, HTIF and TCIF flags in the DMA_ISR register

Loading...

Loading...