DocID13902 Rev 15 1048/1128

RM0008 Ethernet (ETH): media access control (MAC) with DMA controller

1064

Ethernet PTP target time high register (ETH_PTPTTHR)

Address offset: 0x071C

Reset value: 0x0000 0000

This register contains the higher 32 bits of time to be compared with the system time for

interrupt event generation. The Target time high register, along with Target time low register,

is used to schedule an interrupt event (TSARU bit in ETH_PTPTSCR) when the system time

exceeds the value programmed in these registers.

Ethernet PTP target time low register (ETH_PTPTTLR)

Address offset: 0x0720

Reset value: 0x0000 0000

This register contains the lower 32 bits of time to be compared with the system time for

interrupt event generation.

29.8.4 DMA register description

This section defines the bits for each DMA register. Non-32 bit accesses are allowed as long

as the address is word-aligned.

Ethernet DMA bus mode register (ETH_DMABMR)

Address offset: 0x1000

Reset value: 0x0002 0101

The bus mode register establishes the bus operating modes for the DMA.

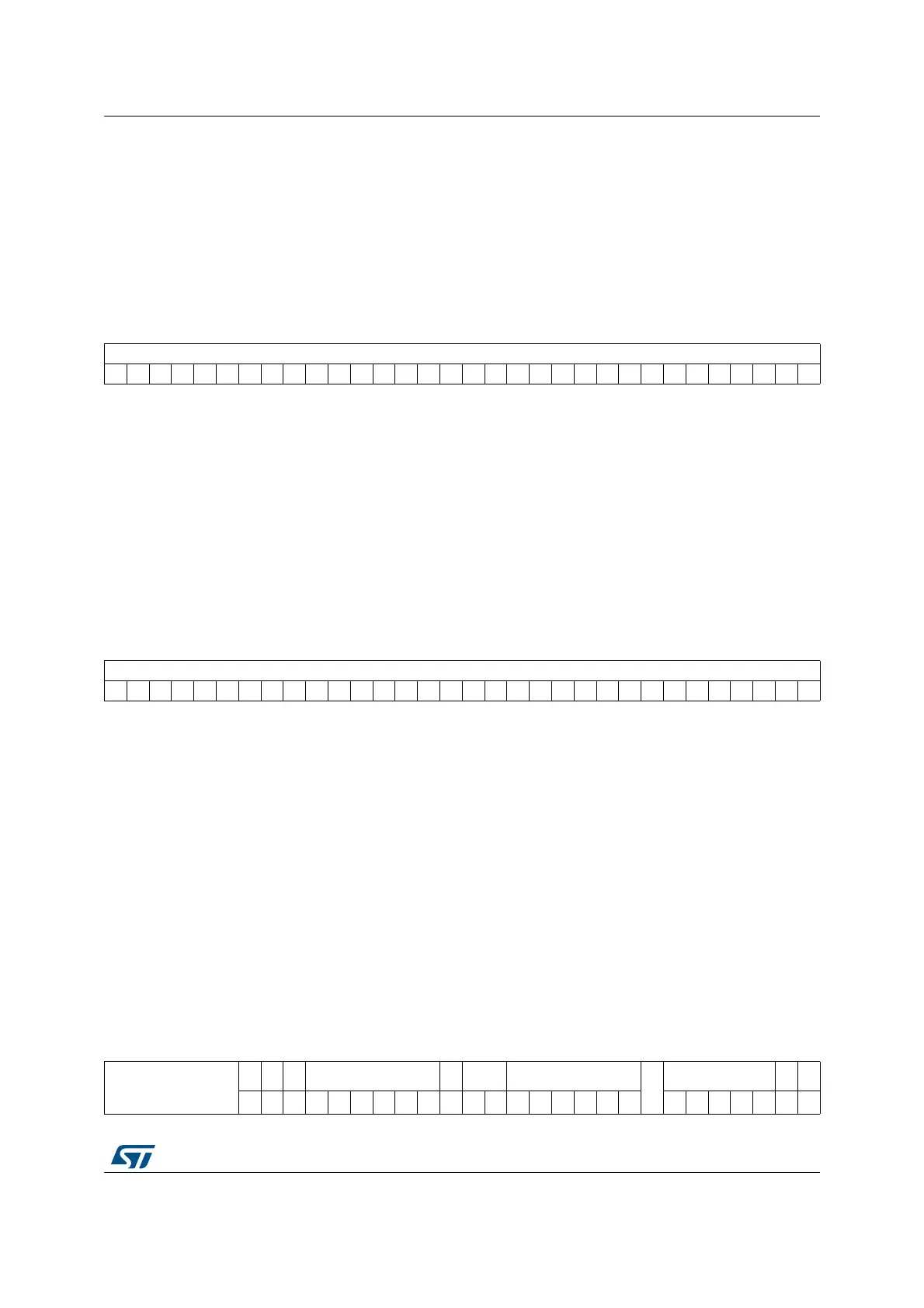

313029282726252423222120191817161514131211109876543210

TTSH

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 TTSH: Target time stamp high

This register stores the time in seconds. When the time stamp value matches or exceeds

both Target time stamp registers, the MAC, if enabled, generates an interrupt.

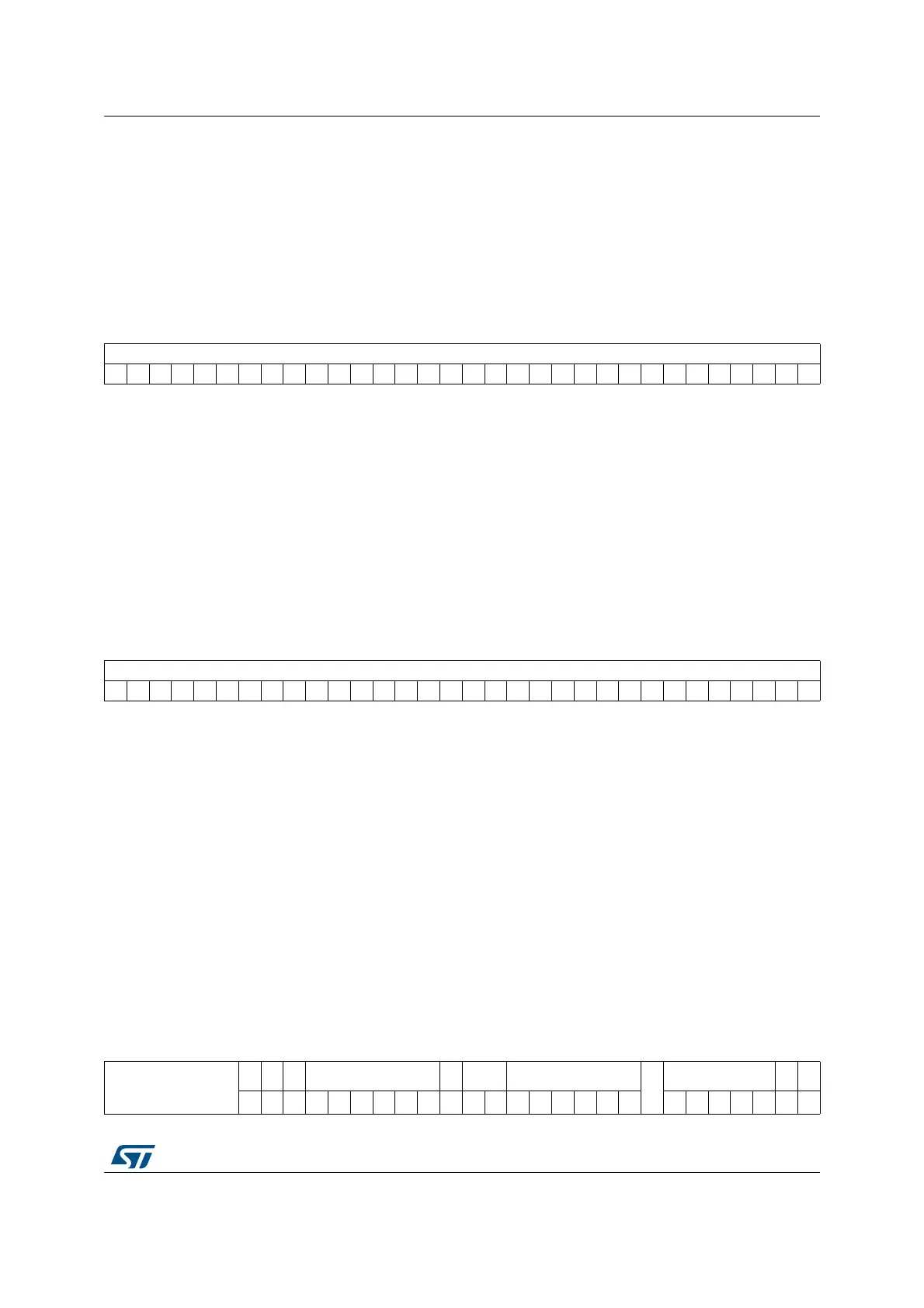

313029282726252423222120191817161514131211109876543210

TTSL

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 TTSL: Target time stamp low

This register stores the time in (signed) nanoseconds. When the value of the time stamp

matches or exceeds both Target time stamp registers, the MAC, if enabled, generates an

interrupt.

313029282726252423222120191817161514131211109876543210

Reserved

AAB

FPM

USP

RDP

FB

PM PBL

Reserved

DSL

DA

SR

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rs

Loading...

Loading...