Ethernet (ETH): media access control (MAC) with DMA controller RM0008

1043/1128 DocID13902 Rev 15

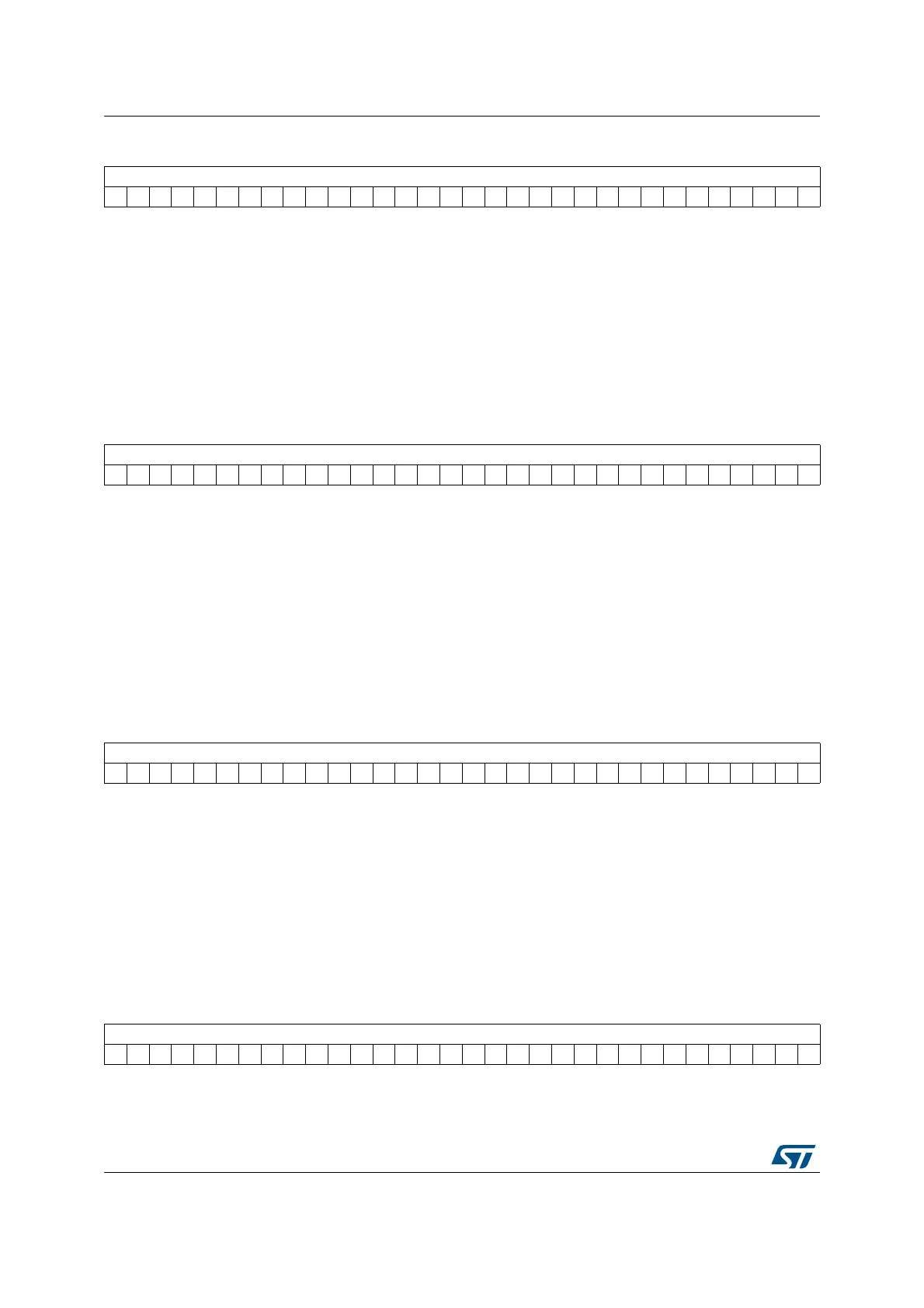

Ethernet MMC received frames with CRC error counter register

(ETH_MMCRFCECR)

Address offset: 0x0194

Reset value: 0x0000 0000

This register contains the number of frames received with CRC error.

Ethernet MMC received frames with alignment error counter register

(ETH_MMCRFAECR)

Address offset: 0x0198

Reset value: 0x0000 0000

This register contains the number of frames received with alignment (dribble) error.

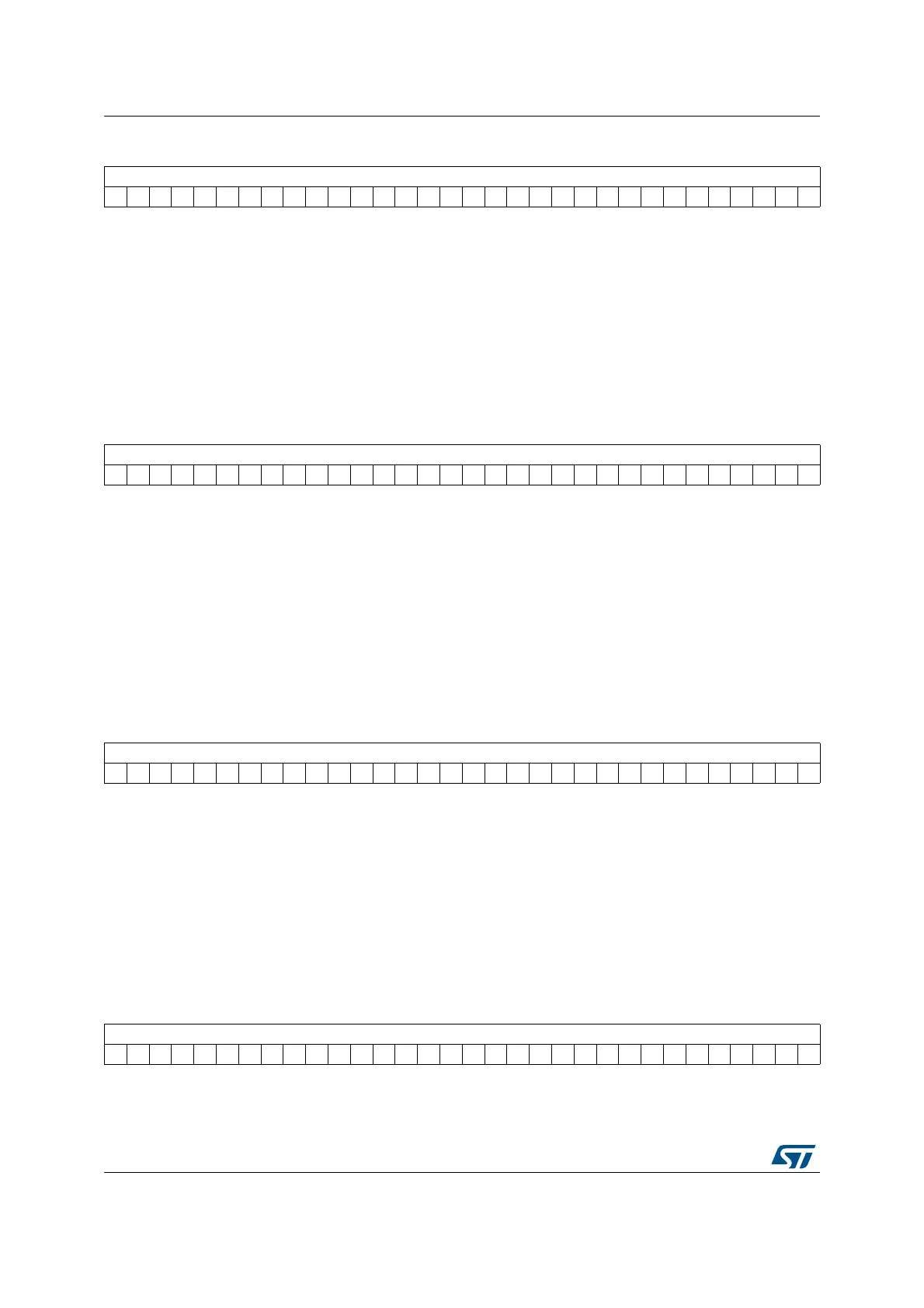

MMC received good unicast frames counter register (ETH_MMCRGUFCR)

Address offset: 0x01C4

Reset value: 0x0000 0000

This register contains the number of good unicast frames received.

313029282726252423222120191817161514131211109876543210

TGFC

rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr

Bits 31:0 TGFC: Transmitted good frames counter

313029282726252423222120191817161514131211109876543210

RFCEC

rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr

Bits 31:0 RFCEC: Received frames CRC error counter

Received frames with CRC error counter

313029282726252423222120191817161514131211109876543210

RFAEC

rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr

Bits 31:0 RFAEC: Received frames alignment error counter

Received frames with alignment error counter

313029282726252423222120191817161514131211109876543210

RGUFC

rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr

Bits 31:0 RGUFC: Received good unicast frames counter

Loading...

Loading...