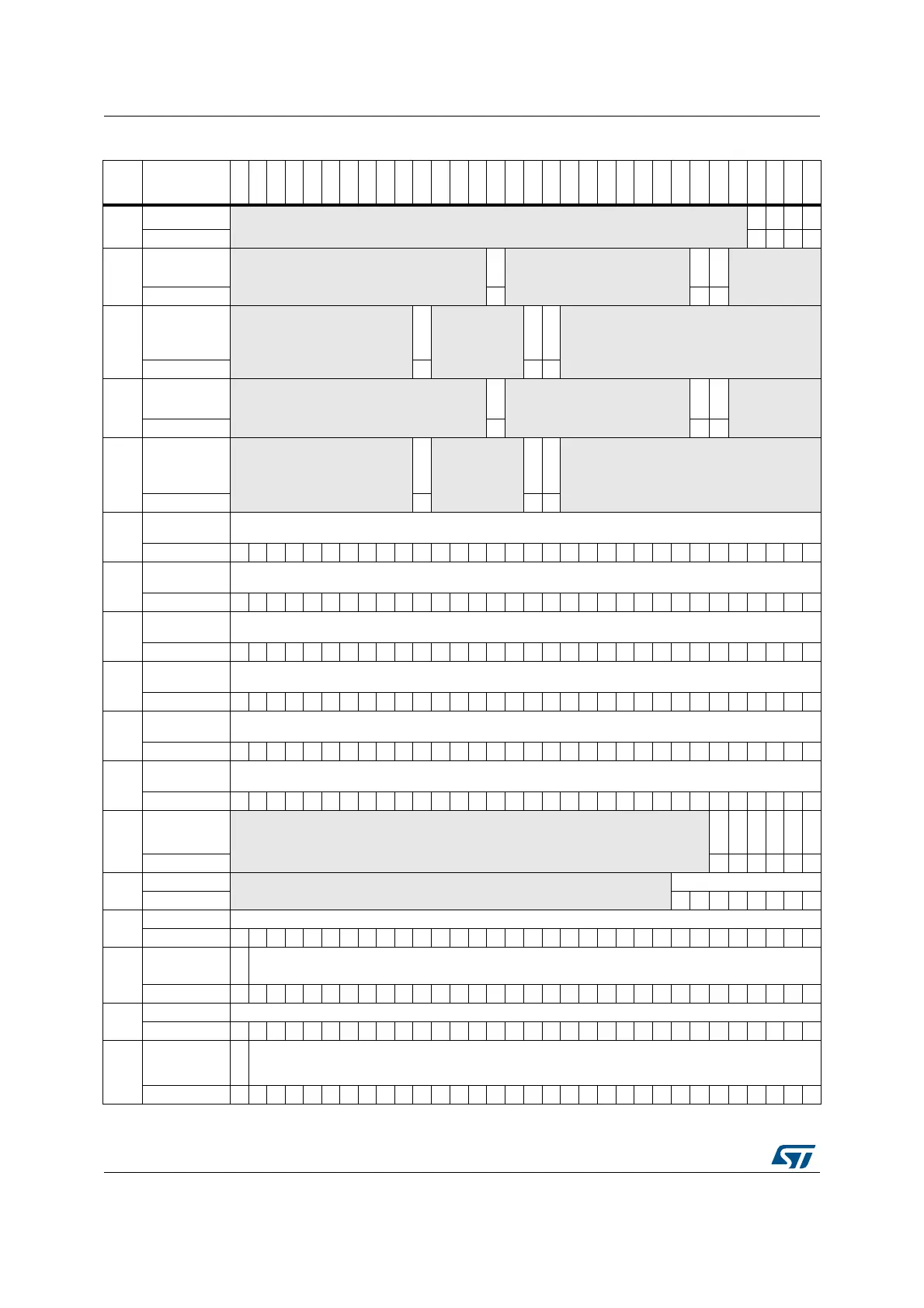

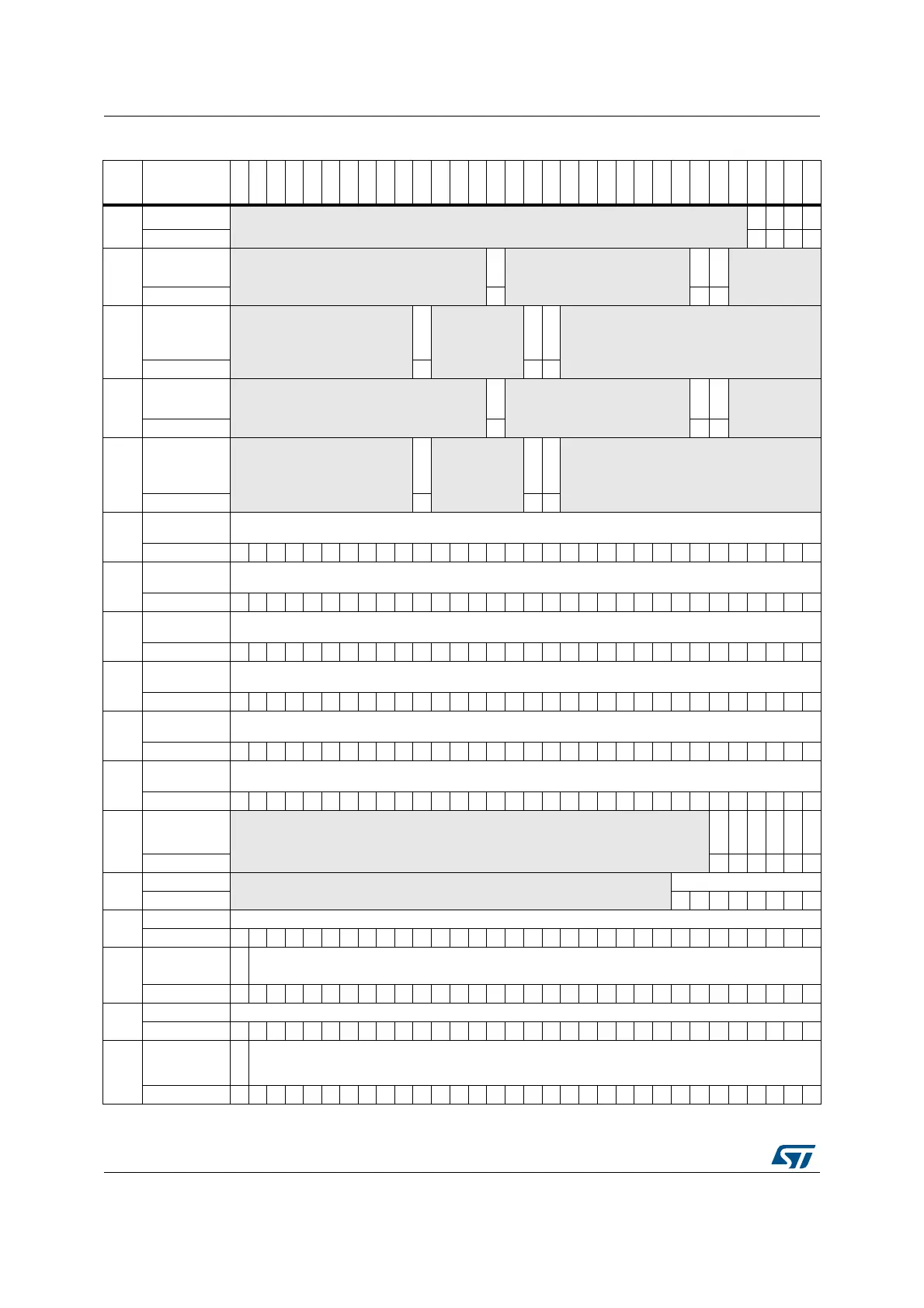

Ethernet (ETH): media access control (MAC) with DMA controller RM0008

1063/1128 DocID13902 Rev 15

0x100

ETH_MMCCR

Reserved

MCF

ROR

CSR

CR

Reset value 0000

0x104

ETH_MMCRIR

Reserved

RGUFS

Reserved

RFAES

RFCES

Reserved

Reset value 000

0x108

ETH_MMCTIR

Reserved

TGFS

Reserved

TGFMSCS

TGFSCS

Reserved

Reset value 000

0x10C

ETH_MMCRIMR

Reserved

RGUFM

Reserved

RFAEM

RFCEM

Reserved

Reset value 000

0x110

ETH_MMCTIMR

Reserved

TGFM

Reserved

TGFMSCM

TGFSCM

Reserved

Reset value 000

0x14C

ETH_MMCTGFS

CCR

TGFSCC

Reset value 00000000000000000000000000 000000

0x150

ETH_MMCTGFM

SCCR

TGFMSCC

Reset value 00000000000000000000000000 000000

0x168

ETH_MMCTGFC

R

TGFC

Reset value 00000000000000000000000000 000000

0x194

ETH_MMCRFCE

CR

RFCEC

Reset value 00000000000000000000000000 000000

0x198

ETH_MMCRFAE

CR

RFAEC

Reset value 00000000000000000000000000 000000

0x1C4

ETH_MMCRGUF

CR

RGUFC

Reset value 00000000000000000000000000 000000

0x700

ETH_PTPTSCR

Reserved

TTSARU

TSITE

TSSTU

TSSTI

TSFCU

TSE

Reset value 000000

0x704

ETH_PTPSSIR

Reserved

STSSI

Reset value 00000000

0x708

ETH_PTPTSHR STS[31:0]

Reset value 00000000000000000000000000 000000

0x70C

ETH_PTPTSLR

STPNS

STSS

Reset value 00000000000000000000000000 000000

0x710

ETH_PTPTSHUR TSUS

Reset value 00000000000000000000000000 000000

0x714

ETH_PTPTSLUR

TSUPNS

TSUSS

Reset value 00000000000000000000000000 000000

Table 217. Ethernet register map and reset values (continued)

Off-

set

Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Loading...

Loading...