Debug support (DBG) RM0008

1079/1128 DocID13902 Rev 15

1011

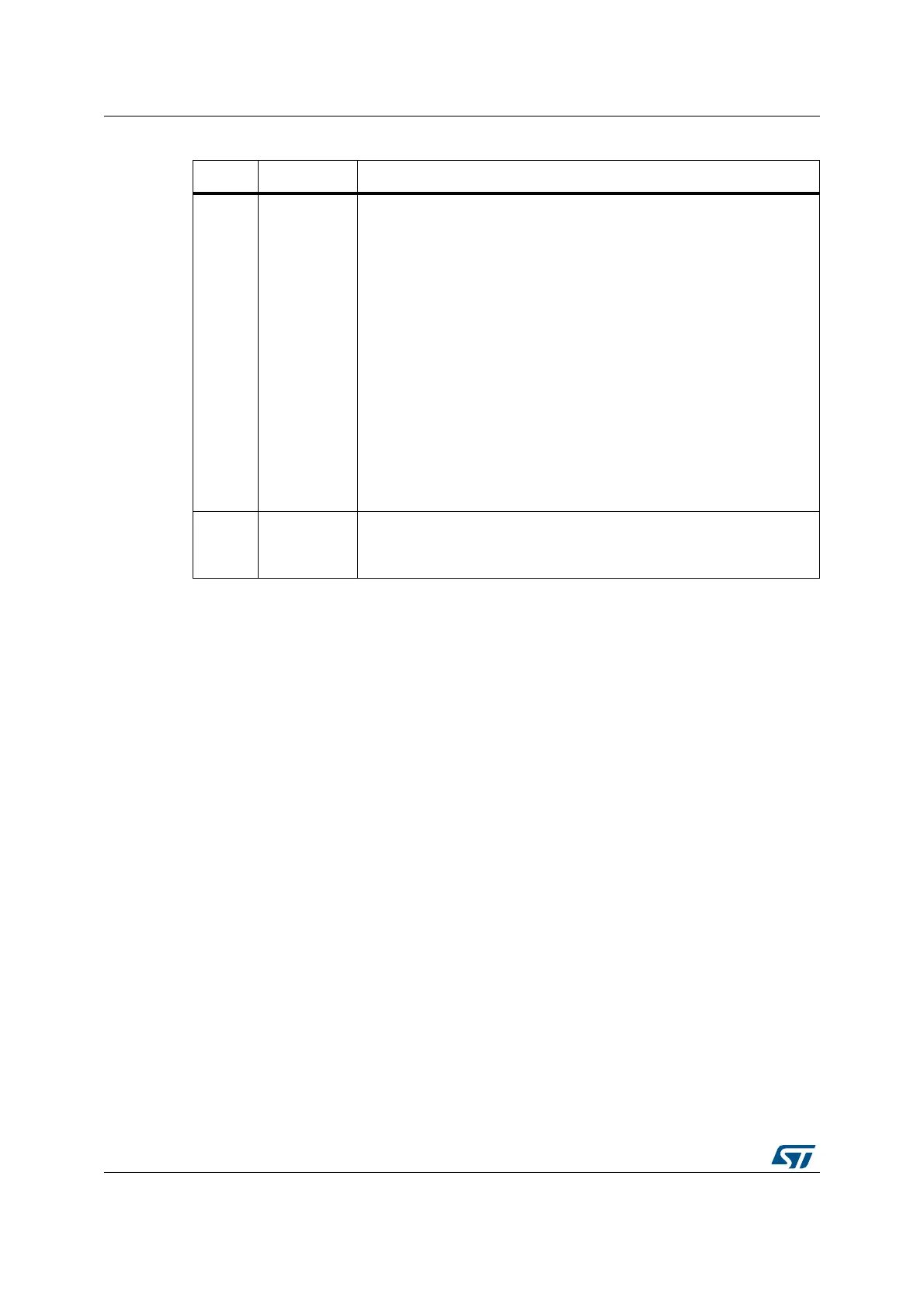

APACC

[35 bits]

Access port access register

Initiates an access port and allows access to an access port register.

– When transferring data IN:

Bits 34:3 = DATA[31:0] = 32-bit data to shift in for a write request

Bits 2:1 = A[3:2] = 2-bit address (sub-address AP registers).

Bit 0 = RnW= Read request (1) or write request (0).

– When transferring data OUT:

Bits 34:3 = DATA[31:0] = 32-bit data which is read following a read

request

Bits 2:0 = ACK[2:0] = 3-bit Acknowledge:

010 = OK/FAULT

001 = WAIT

OTHER = reserved

There are many AP Registers (see AHB-AP) addressed as the

combination of:

– The shifted value A[3:2]

– The current value of the DP SELECT register

1000

ABORT

[35 bits]

Abort register

– Bits 31:1 = Reserved

– Bit 0 = DAPABORT: write 1 to generate a DAP abort.

Table 220. JTAG debug port data registers (continued)

IR(3:0) Data register Details

Loading...

Loading...