Low-, medium-, high- and XL-density reset and clock control (RCC) RM0008

113/1128 DocID13902 Rev 15

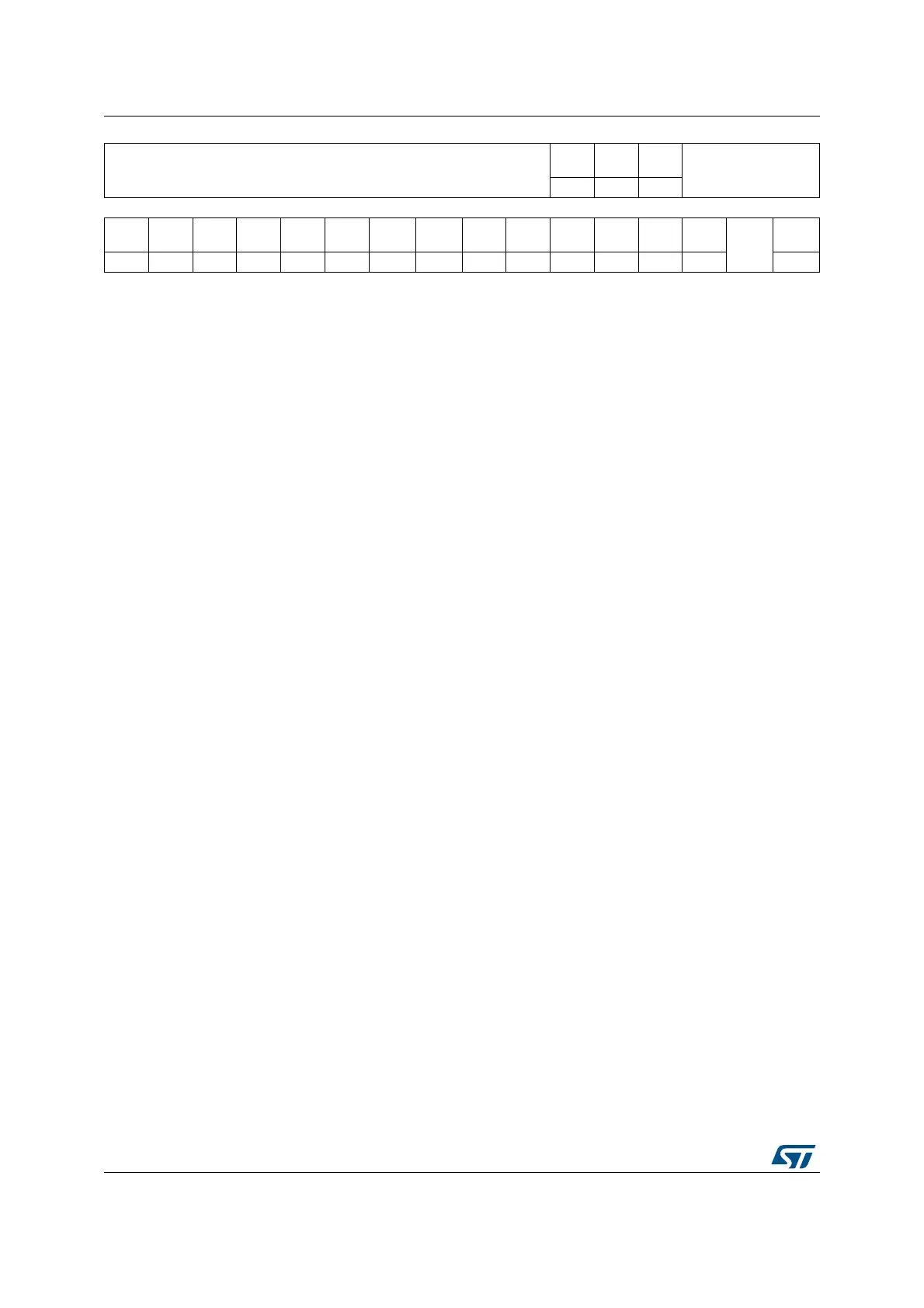

Reserved

TIM11

EN

TIM10

EN

TIM9

EN

Reserved

rw rw rw

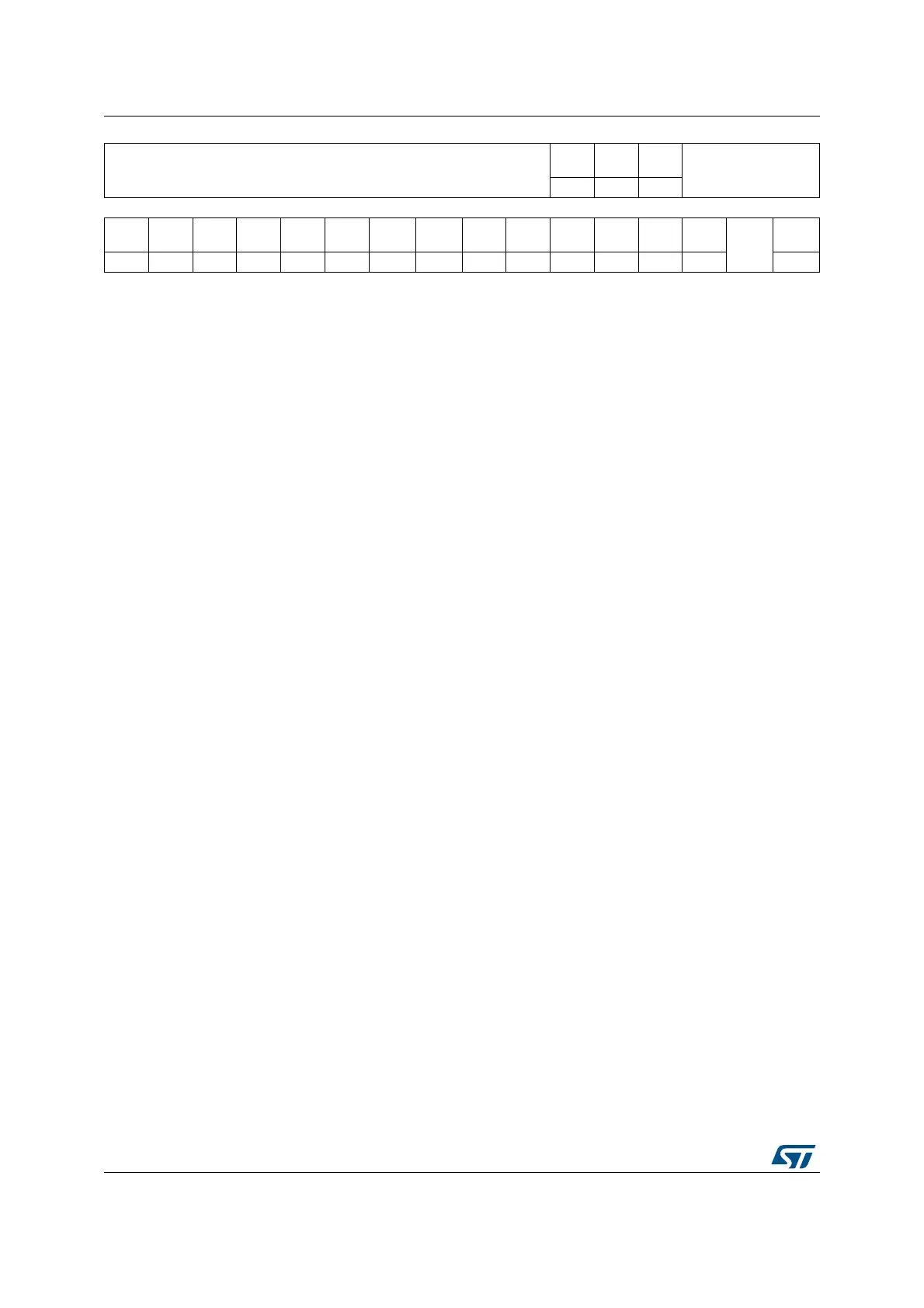

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

ADC3

EN

USART

1EN

TIM8

EN

SPI1

EN

TIM1

EN

ADC2

EN

ADC1

EN

IOPG

EN

IOPF

EN

IOPE

EN

IOPD

EN

IOPC

EN

IOPB

EN

IOPA

EN

Res.

AFIO

EN

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:22 Reserved, must be kept at reset value.

Bit 21 TIM11EN: TIM11 timer clock enable

Set and cleared by software.

0: TIM11 timer clock disabled

1: TIM11 timer clock enabled

Bit 20 TIM10EN: TIM10 timer clock enable

Set and cleared by software.

0: TIM10 timer clock disabled

1: TIM10 timer clock enabled

Bit 19 TIM9EN: TIM9 timer clock enable

Set and cleared by software.

0: TIM9 timer clock disabled

1: TIM9 timer clock enabled

Bits 18:16 Reserved, always read as 0.

Bit 15 ADC3EN: ADC3 interface clock enable

Set and cleared by software.

0: ADC3 interface clock disabled

1: ADC3 interface clock enabled

Bit 14 USART1EN: USART1 clock enable

Set and cleared by software.

0: USART1 clock disabled

1: USART1 clock enabled

Bit 13 TIM8EN: TIM8 Timer clock enable

Set and cleared by software.

0: TIM8 timer clock disabled

1: TIM8 timer clock enabled

Bit 12 SPI1EN: SPI1 clock enable

Set and cleared by software.

0: SPI1 clock disabled

1: SPI1 clock enabled

Bit 11 TIM1EN: TIM1 timer clock enable

Set and cleared by software.

0: TIM1 timer clock disabled

1: TIM1 timer clock enabled

Bit 10 ADC2EN: ADC 2 interface clock enable

Set and cleared by software.

0: ADC 2 interface clock disabled

1: ADC 2 interface clock enabled

Loading...

Loading...