Memory and bus architecture RM0008

53/1128 DocID13902 Rev 15

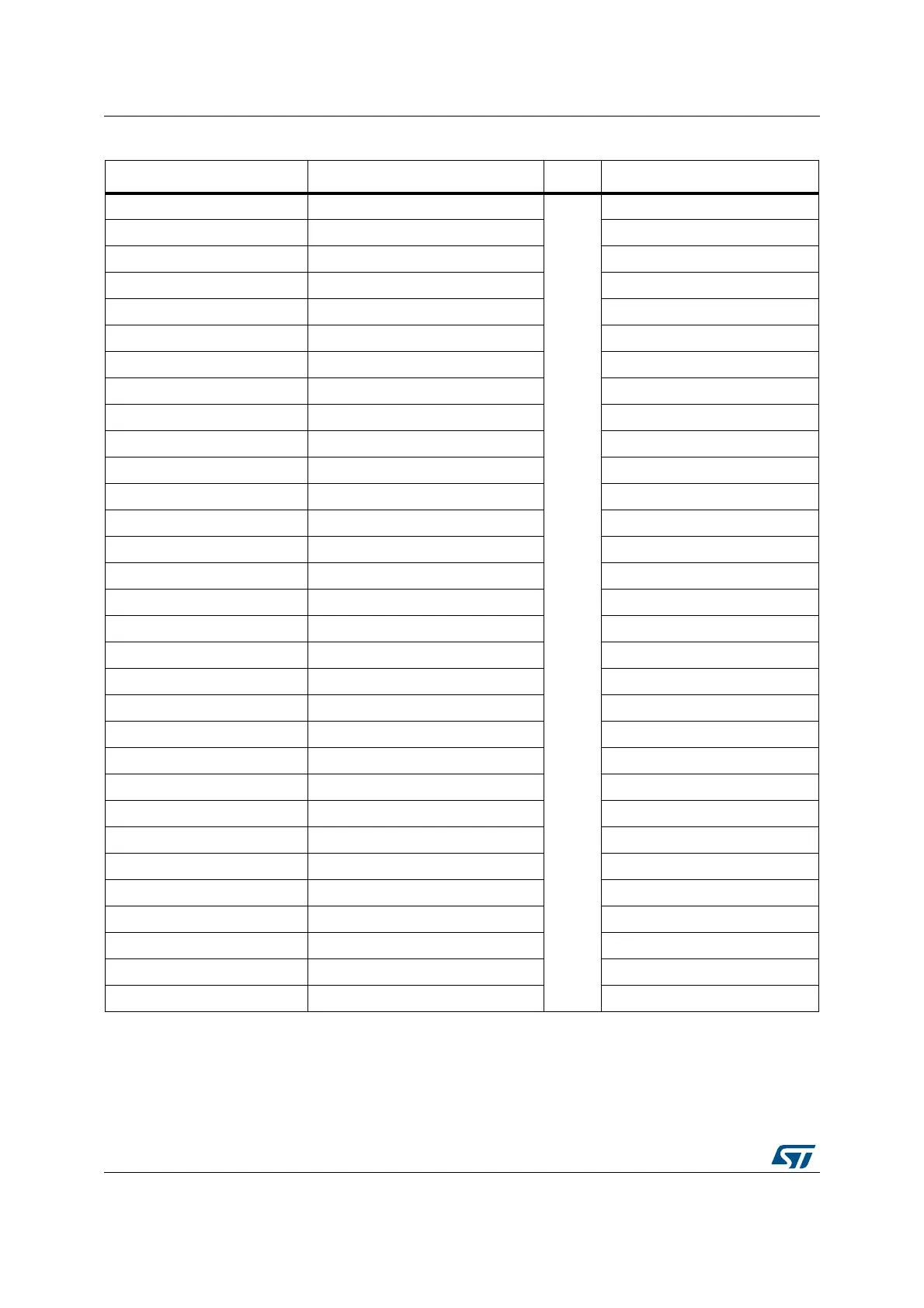

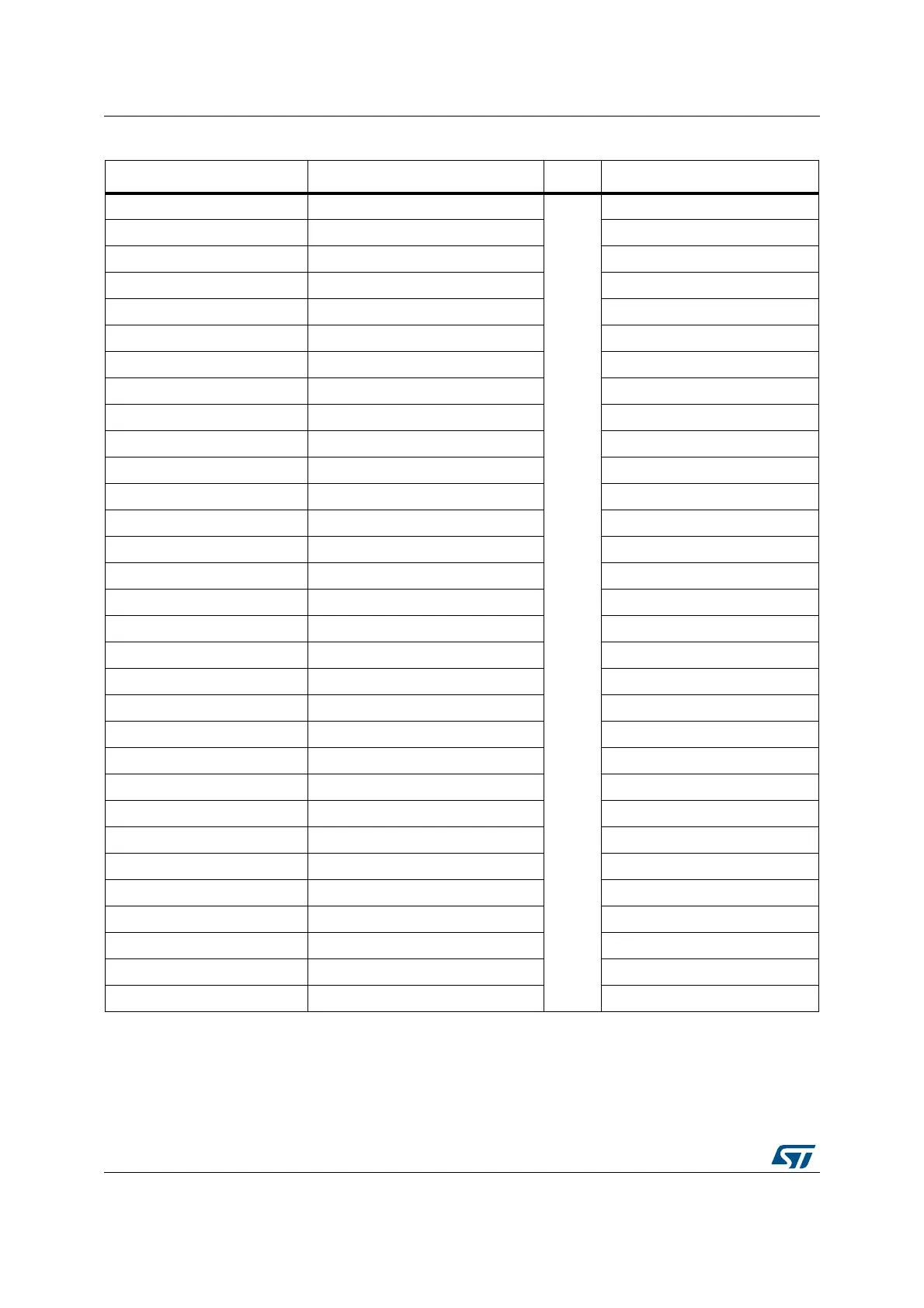

0x4000 7800 - 0x4000 FFFF Reserved

APB1

0x4000 7400 - 0x4000 77FF DAC Section 12.5.14 on page 272

0x4000 7000 - 0x4000 73FF Power control PWR Section 5.4.3 on page 80

0x4000 6C00 - 0x4000 6FFF Backup registers (BKP) Section 6.4.5 on page 85

0x4000 6400 - 0x4000 67FF bxCAN1 Section 24.9.5 on page 686

0x4000 6800 - 0x4000 6BFF bxCAN2 Section 24.9.5 on page 686

0x4000 6000

(1)

- 0x4000 63FF Shared USB/CAN SRAM 512 bytes

0x4000 5C00 - 0x4000 5FFF USB device FS registers Section 23.5.4 on page 643

0x4000 5800 - 0x4000 5BFF I2C2 Section 26.6.10 on page 777

0x4000 5400 - 0x4000 57FF I2C1 Section 26.6.10 on page 777

0x4000 5000 - 0x4000 53FF UART5 Section 27.6.8 on page 820

0x4000 4C00 - 0x4000 4FFF UART4 Section 27.6.8 on page 820

0x4000 4800 - 0x4000 4BFF USART3 Section 27.6.8 on page 820

0x4000 4400 - 0x4000 47FF USART2 Section 27.6.8 on page 820

0x4000 4000 - 0x4000 43FF Reserved

0x4000 3C00 - 0x4000 3FFF SPI3/I2S Section 25.5 on page 733

0x4000 3800 - 0x4000 3BFF SPI2/I2S Section 25.5 on page 733

0x4000 3400 - 0x4000 37FF Reserved

0x4000 3000 - 0x4000 33FF Independent watchdog (IWDG) Section 19.4.5 on page 490

0x4000 2C00 - 0x4000 2FFF Window watchdog (WWDG) Section 20.6.4 on page 497

0x4000 2800 - 0x4000 2BFF RTC Section 18.4.7 on page 484

0x4000 2400 - 0x4000 27FF Reserved

0x4000 2000 - 0x4000 23FF TIM14 timer Section 16.5.10 on page 459

0x4000 1C00 - 0x4000 1FFF TIM13 timer Section 16.5.10 on page 459

0x4000 1800 - 0x4000 1BFF TIM12 timer Section 16.4.13 on page 449

0x4000 1400 - 0x4000 17FF TIM7 timer Section 17.4.9 on page 472

0x4000 1000 - 0x4000 13FF TIM6 timer Section 17.4.9 on page 472

0x4000 0C00 - 0x4000 0FFF TIM5 timer Section 15.4.19 on page 416

0x4000 0800 - 0x4000 0BFF TIM4 timer Section 15.4.19 on page 416

0x4000 0400 - 0x4000 07FF TIM3 timer Section 15.4.19 on page 416

0x4000 0000 - 0x4000 03FF TIM2 timer Section 15.4.19 on page 416

1. This shared SRAM can be fully accessed only in low-, medium-, high- and XL-density devices, not in connectivity line

devices.

Table 3. Register boundary addresses (continued)

Boundary address Peripheral Bus Register map

Loading...

Loading...