DocID13902 Rev 15 684/1128

RM0008 Controller area network (bxCAN)

689

Note: Please refer to Figure 229: Filter bank scale configuration - register organization on

page 657.

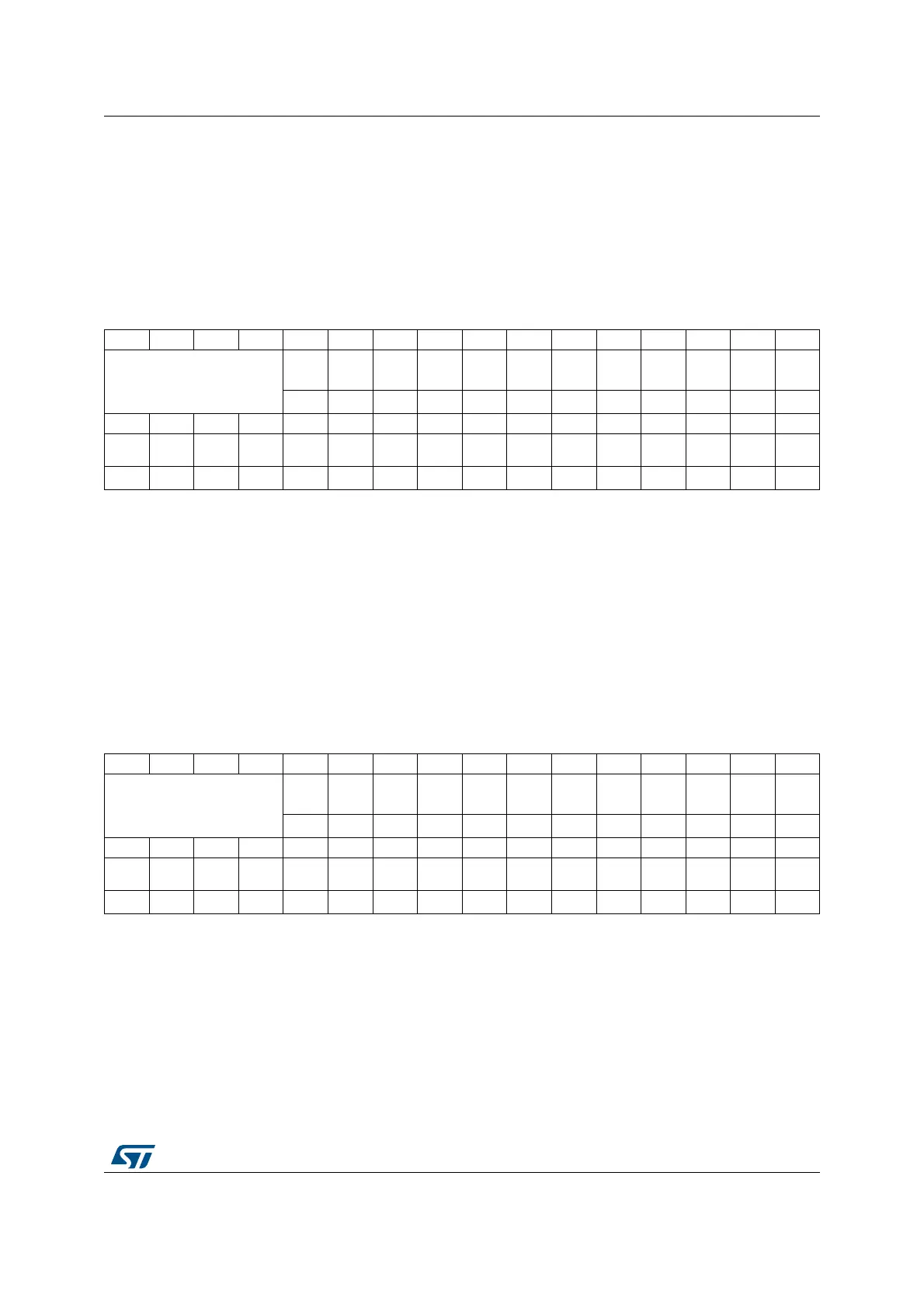

CAN filter FIFO assignment register (CAN_FFA1R)

Address offset: 0x214

Reset value: 0x0000 0000

This register can be written only when the filter initialization mode is set (FINIT=1) in the

CAN_FMR register.

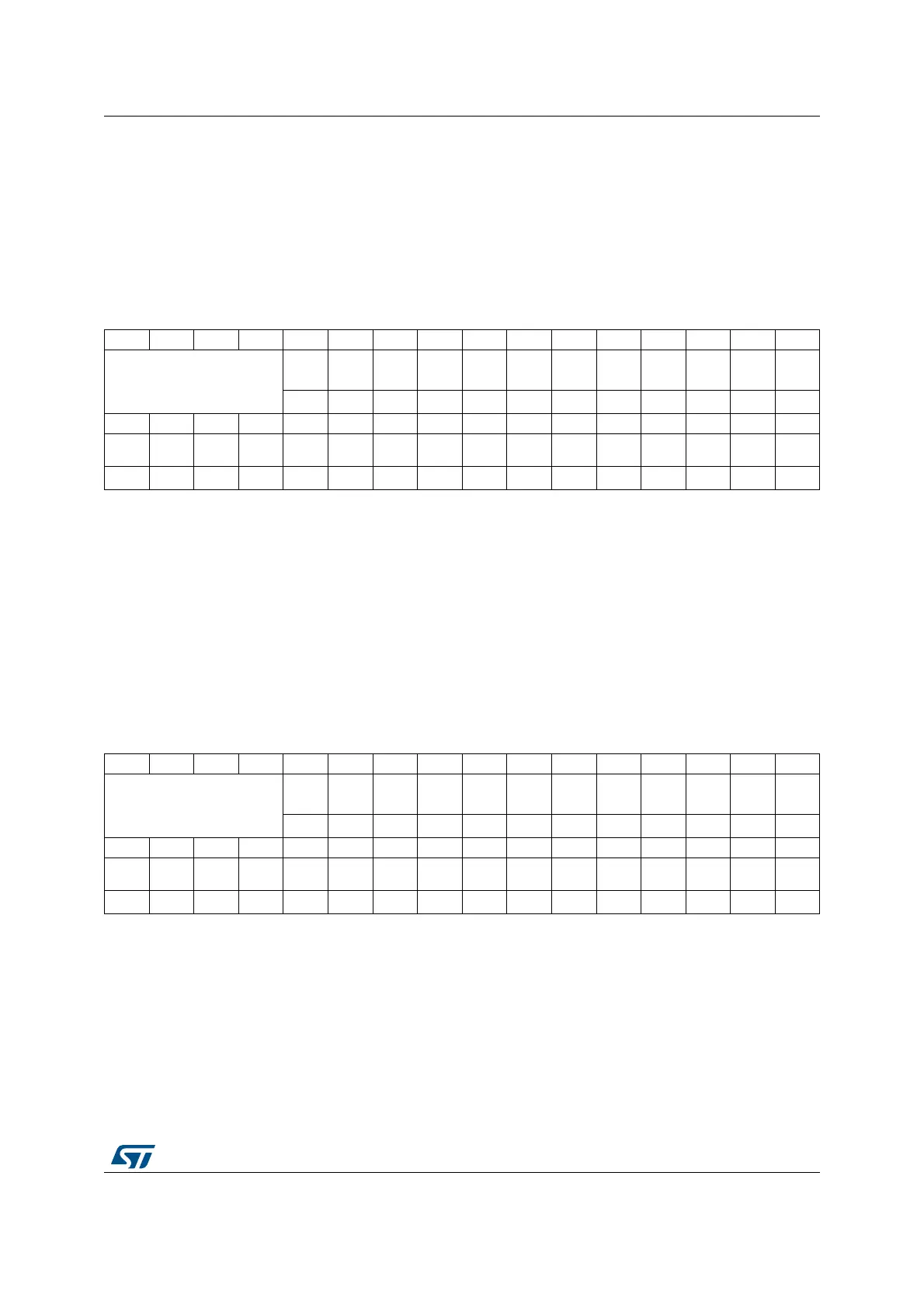

CAN filter activation register (CAN_FA1R)

Address offset: 0x21C

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

FFA2

7

FFA2

6

FFA2

5

FFA2

4

FFA2

3

FFA2

2

FFA2

1

FFA2

0

FFA1

9

FFA1

8

FFA1

7

FFA1

6

rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

FFA15 FFA14 FFA13 FFA12 FFA11 FFA10 FFA9 FFA8 FFA7 FFA6 FFA5 FFA4 FFA3 FFA2 FFA1 FFA0

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:28 Reserved, must be kept at reset value.

Bits 27:0 FFAx

: Filter FIFO assignment for filter x

The message passing through this filter will be stored in the specified FIFO.

0: Filter assigned to FIFO 0

1: Filter assigned to FIFO 1

Note: Bits 27:14 are available in connectivity line devices only and are reserved otherwise.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

FACT

27

FACT

26

FACT

25

FACT

24

FACT

23

FACT

22

FACT

21

FACT

20

FACT

19

FACT

18

FACT

17

FACT

16

rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

FACT15 FACT14 FACT13 FACT12 FACT11 FACT10 FACT9 FACT8 FACT7 FACT6 FACT5 FACT4 FACT3 FACT2 FACT1 FACT0

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:28 Reserved, must be kept at reset value.

Bits 27:0 FACTx

: Filter active

The software sets this bit to activate Filter x. To modify the Filter x registers (CAN_FxR[0:7]),

the FACTx bit must be cleared or the FINIT bit of the CAN_FMR register must be set.

0: Filter x is not active

1: Filter x is active

Note: Bits 27:14 are available in connectivity line devices only and are reserved otherwise.

Loading...

Loading...