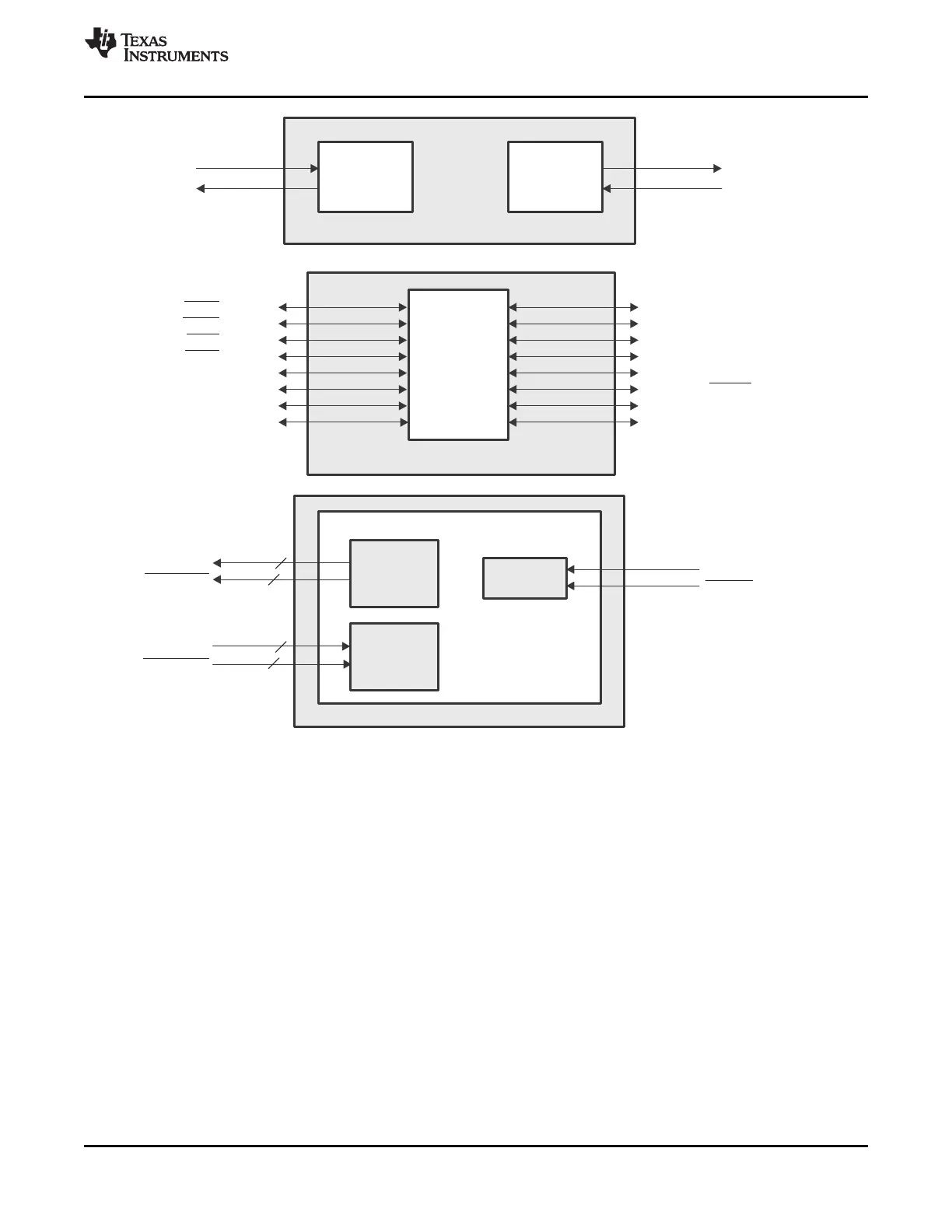

TINPL1

TOUTL1

URADDR3/ /GP[15]PREQ

(C)

Timer 1 Timer 2

Timers (64-Bit)

URADDR2/ /GP[14]PINTA

(C)

URADDR1/ /GP[13]PRST

(C)

URADDR0/ /GP[12]PGNT

(C)

FSX1/GP[11]

(B)

FSR1/GP[10]

(B)

DX1/GP[9]

(B)

DR1/GP[8]

(B)

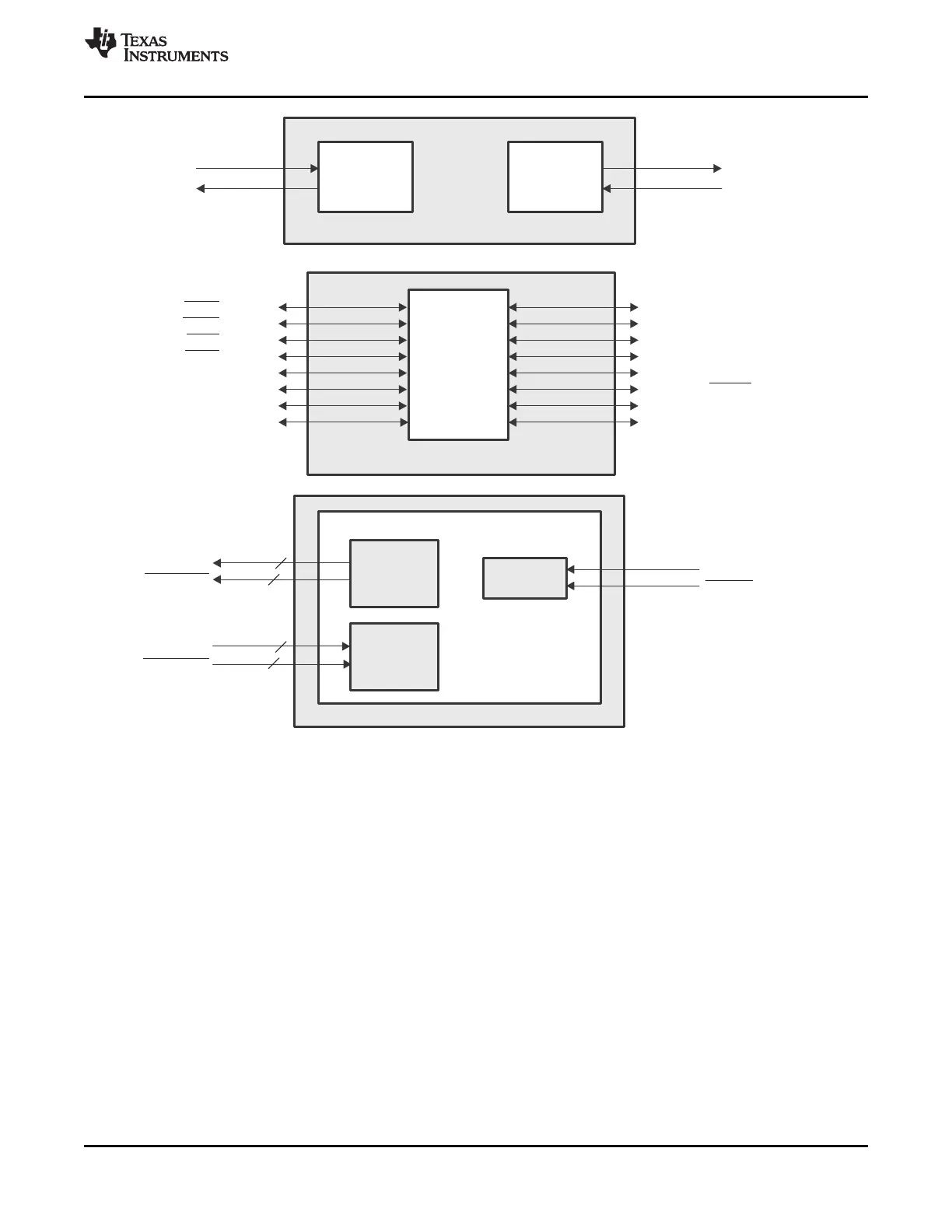

GPIO

General-Purpose Input/Output (GPIO) Port 0

RIOTX[3:0]

RIOTX[3:0]

RIORX[3:0]

RIORX[3:0]

4

4

4

4

Transmit

Receive

Clock

RapidIO

RIOCLK

RIOCLK

A. This pin functions as GP[1] by default.

B. These McBSP1 peripheral pins are muxed with the GPIO peripheral pins and, by default, these signals function as GPIO peripheral

pins. For more details, see the section of this document.Device Configuration

C. These UTOPIA and PCI peripheral pins are muxed with the GPIO peripheral pins and, by default, these signals function as GPIO

peripheral pins. For more details, see the section of this document.Device Configuration

GP[7]

GP[6]

GP[5]

GP[4]

CLKX1/GP[3]

(B)

URADDR4/ /GP[2]PCBE0

(C)

SYSCLK4/GP[1]

(A)

CLKR1/GP[0]

(B)

TINPL0

TOUTL0

TMS320C6455

www.ti.com

SPRS276M –MAY 2005–REVISED MARCH 2012

Figure 2-7. Timers/GPIO/RapidIO Peripheral Signals

Copyright © 2005–2012, Texas Instruments Incorporated Device Overview 21

Submit Documentation Feedback

Product Folder Link(s): TMS320C6455

Loading...

Loading...