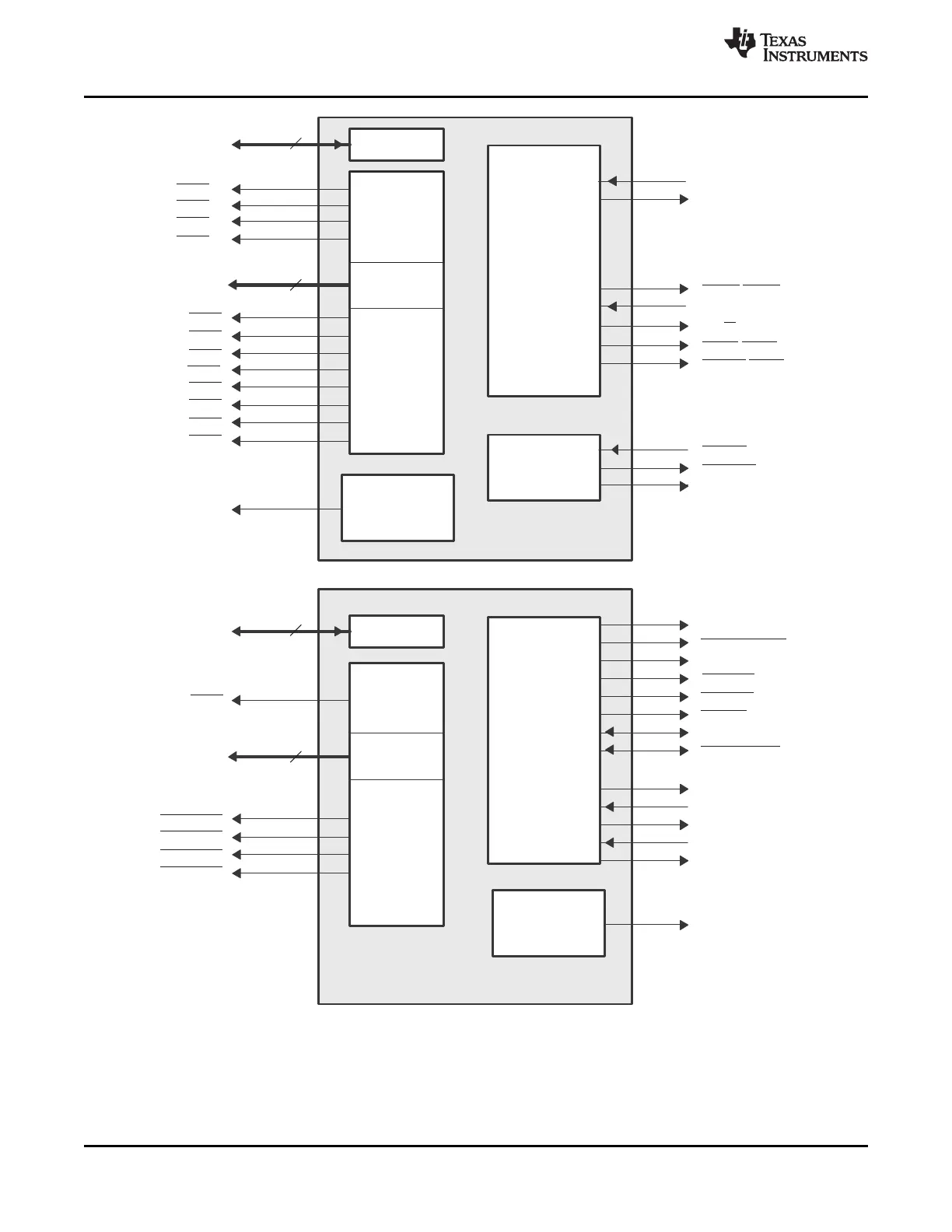

ACE4

(A)

AECLKOUT

AED[63:0]

ACE3

(A)

ACE2

(A)

AEA[19:0]

AARDY

Data

Memory Map

Space Select

Address

Byte Enables

64

20

External

Memory I/F

Control

EMIFA (64-bit Data Bus)

AECLKIN

AHOLD

AHOLDA

ABUSREQ

Bus

Arbitration

ABE3

ABE2

ABE1

ABE0

ASWE/AAWE

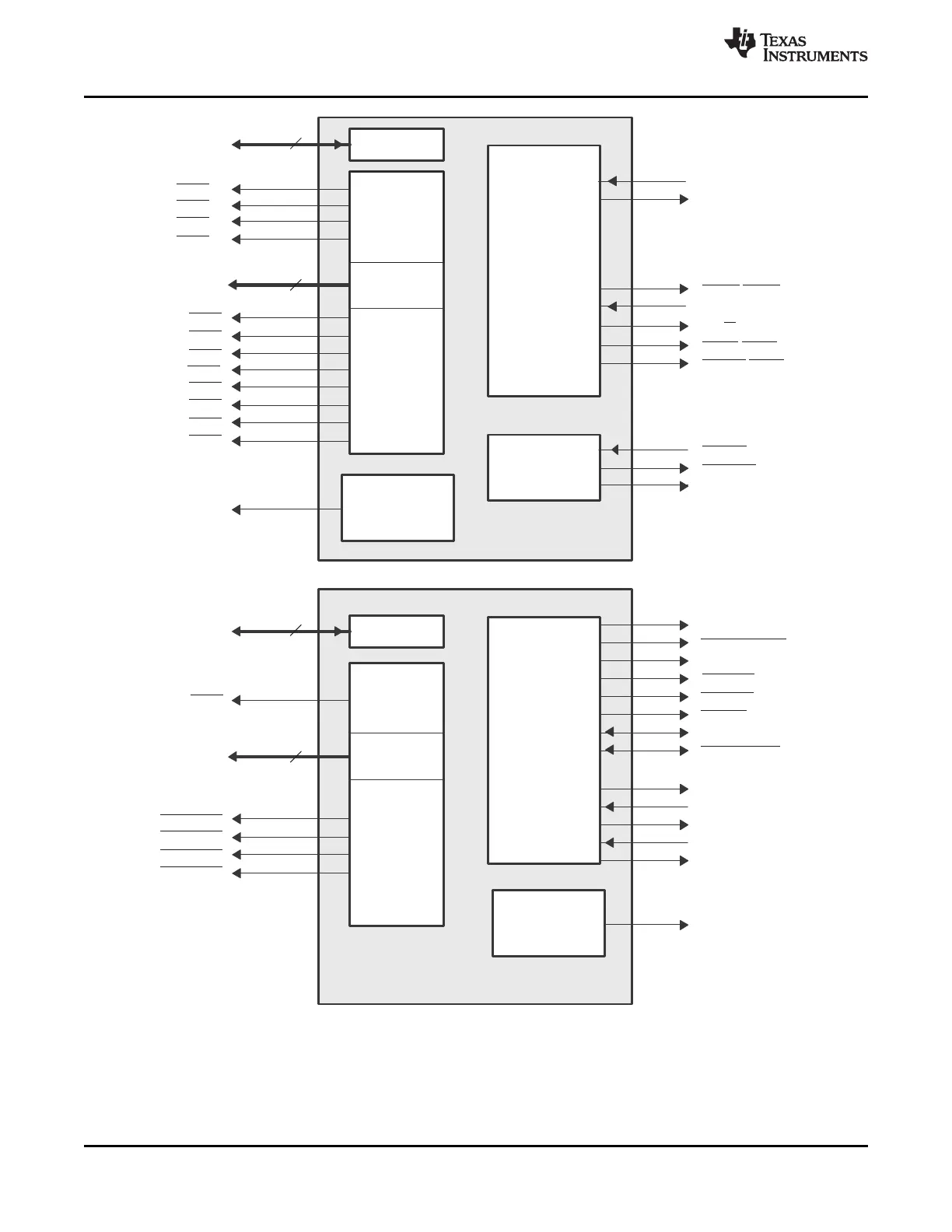

DDR2CLKOUT

DED[31:0]

DCE0

DEA[13:0]

Data

Memory Map

Space Select

Address

Byte Enables

32

14

External

Memory I/F

Control

DDR2 Memoty Controller (32-bit Data Bus)

DSDCAS

DSDCKE

DDR2CLKOUT

DSDDQS[3:0]

DSDRAS

DSDWE

DSDDQS[3:0]

ABE7

ABE6

ABE5

ABE4

ACE5

(A)

Bank Address

ABA[1:0]

AR/W

AAOE/ASOE

ASADS/ASRE

Bank Address

DBA[2:0]

DEODT[1:0]

DSDDQGATE[0]

DSDDQM3

DSDDQM2

DSDDQM1

DSDDQM0

DSDDQGATE[1]

DSDDQGATE[2]

DSDDQGATE[3]

TMS320C6455

SPRS276M –MAY 2005–REVISED MARCH 2012

www.ti.com

Figure 2-8. EMIFA and DDR2 Memory Controller Peripheral Signals

22 Device Overview Copyright © 2005–2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320C6455

Loading...

Loading...