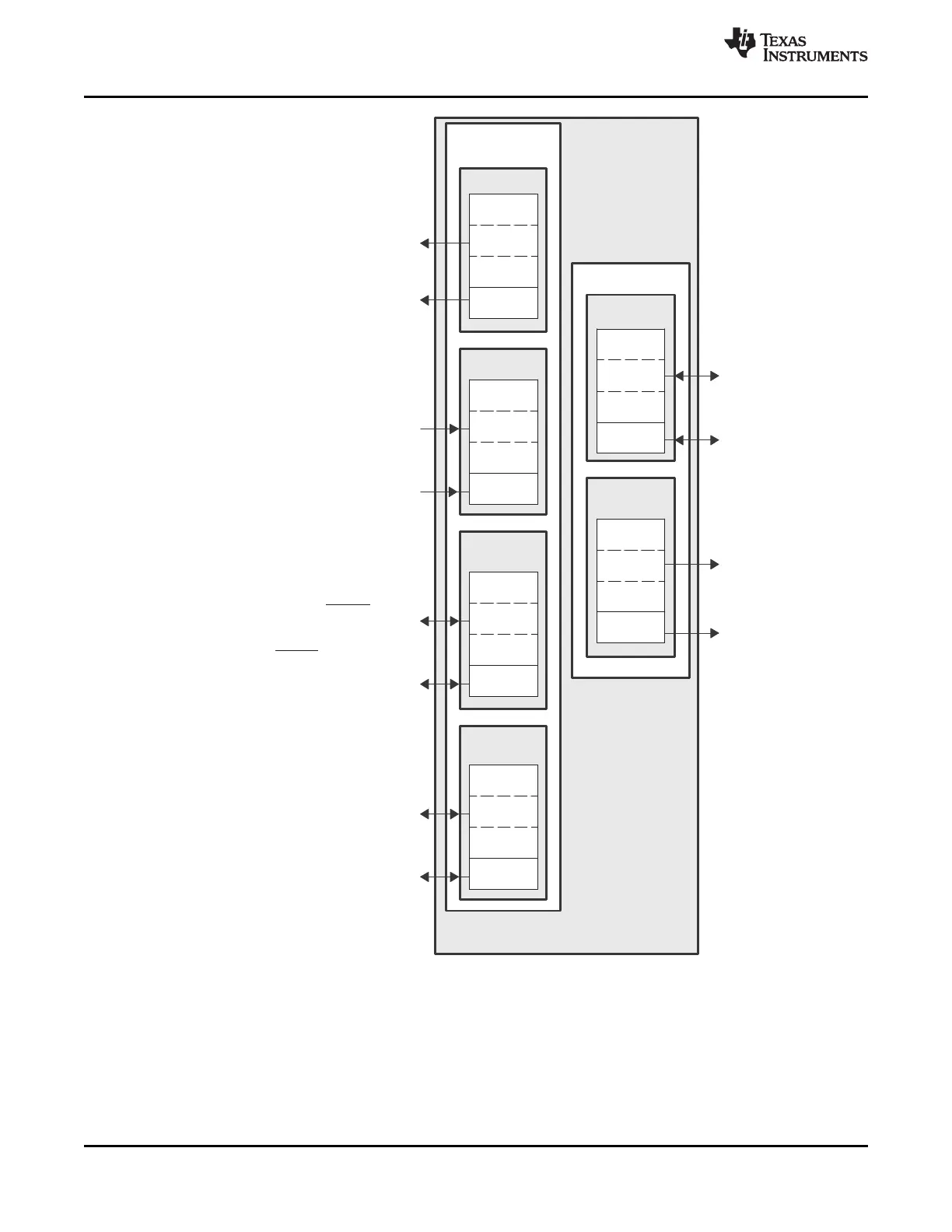

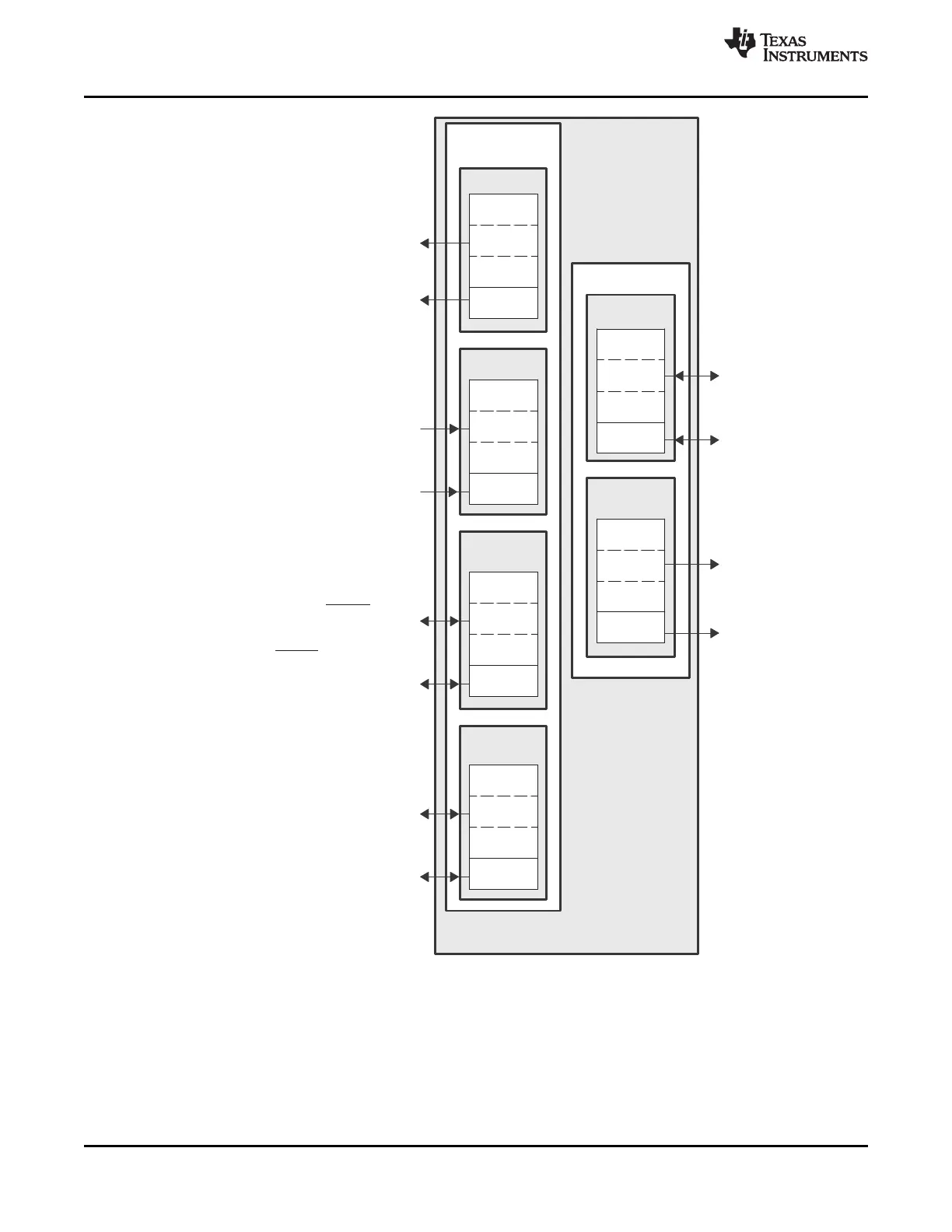

RGTXCTL, RGRXCTL

URSOC/MRXER/RMRXER,

URENB

/MRXDV,

URCLAV/MCRS/RMCRSDV,

UXSOC/MCOL,

UXENB

/MTXEN/RMTXEN

Ethernet MAC (EMAC) and MDIO

(B)

UXADDR3/MDIO

UXADDR4/MDCLK

MDIO

Clock

Clocks

Error Detect

and Control

Input/Output

Receive

RGMDIO

RGMDCLK

RGTXD[3:0]

A. RGMII signals are mutually exclusive to all other EMAC signals.

B. These EMAC pins are muxed with the UTOPIA peripheral. By default, these signals function as EMAC. For more details on these

muxed pins, see the Device Configuration section of this document.

RGTXC,

RGRXC,

RGREFCLK

UXDATA[7:2]/MTXD[7:2],

UXDATA[1:0]/MTXD[1:0]/RMTXD[1:0]

Transmit

RGMII

(A)

GMII

RMII

MII

RGRXD[3:0]

URDATA[7:2]/MRXD[7:2],

URDATA[1:0]/MRXD[1:0]/RMRXD[1:0]

RGMII

(A)

GMII

RMII

MII

RGMII

(A)

GMII

RMII

MII

RGMII

(A)

GMII

RMII

MII

RGMII

(A)

GMII

RMII

MII

GMII

RMII

MII

RGMII

(A)

UXCLK/MTCLK/RMREFCLK,

URCLK/MRCLK,

UXCLAV/GMTCLK

Ethernet MAC

(EMAC)

TMS320C6455

SPRS276M –MAY 2005–REVISED MARCH 2012

www.ti.com

Figure 2-10. EMAC/MDIO [MII, GMII, RMII, and RGMII] Peripheral Signals

24 Device Overview Copyright © 2005–2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320C6455

Loading...

Loading...