TMS320C6455

www.ti.com

SPRS276M –MAY 2005–REVISED MARCH 2012

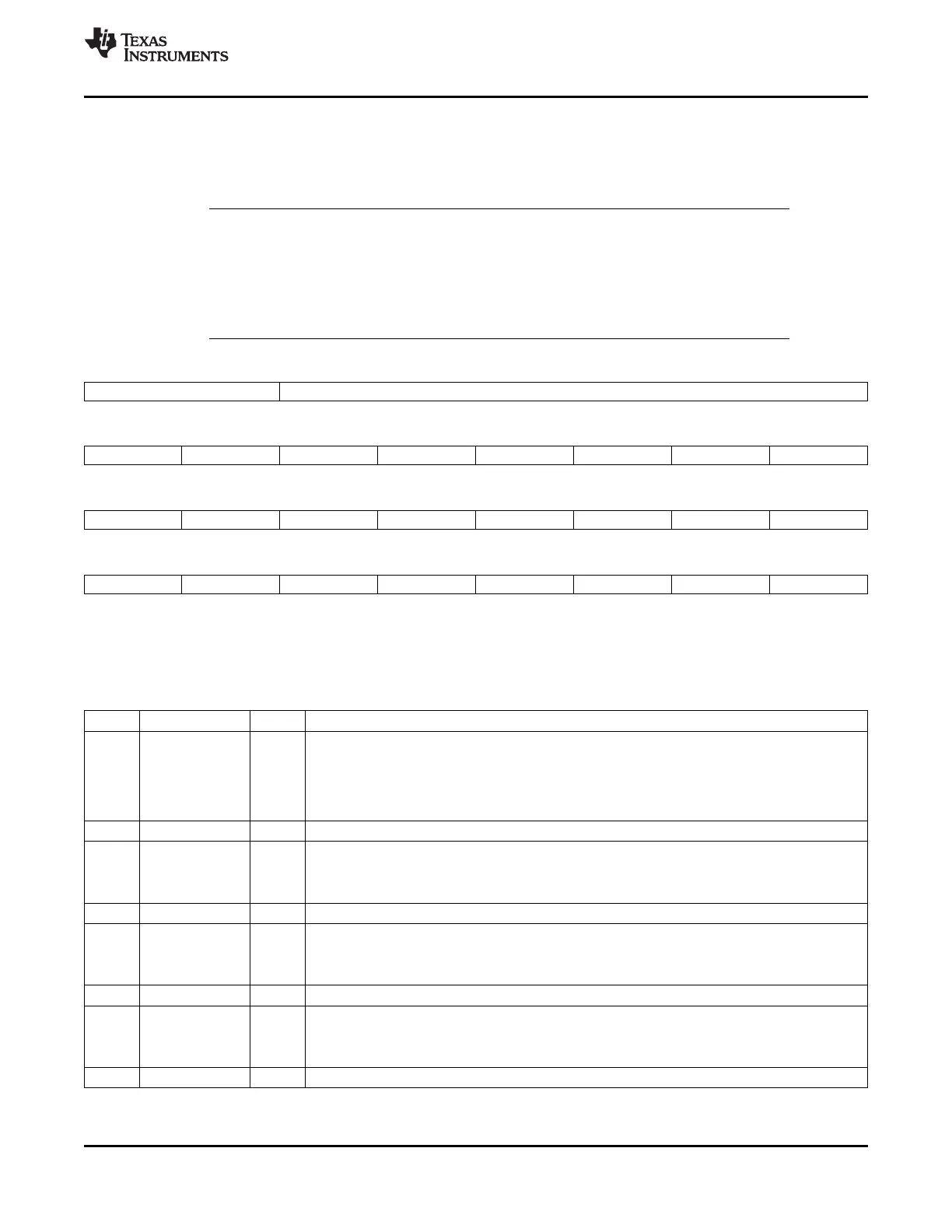

3.4.2 Peripheral Configuration Register 0 Description

The Peripheral Configuration Register (PERCFG0) is used to change the state of the peripherals. One

write is allowed to this register within 16 SYSCLK3 cycles after the correct key is written to the PERLOCK

register.

NOTE

The instructions that write to the PERLOCK and PERCFG0 registers must be in the same

fetch packet if code is being executed from external memory. If the instructions are in

different fetch packets, fetching the second instruction from external memory may stall the

instruction long enough that the PERCFG0 register is locked before the instruction is

executed.

31 30 29 24

SRIOCTL Reserved

R/W-0 R/W-0

23 22 21 20 19 18 17 16

Reserved UTOPIACTL Reserved PCICTL Reserved HPICTL Reserved McBSP1CTL

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

15 14 13 12 11 10 9 8

Reserved McBSP0CTL Reserved I2CCTL Reserved GPIOCTL Reserved TIMER1CTL

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

7 6 5 4 3 2 1 0

Reserved TIMER0CTL Reserved EMACCTL Reserved VCPCTL Reserved TCPCTL

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; -n = value after reset

Figure 3-4. Peripheral Configuration Register 0 (PERCFG0) - 0x02AC 0008

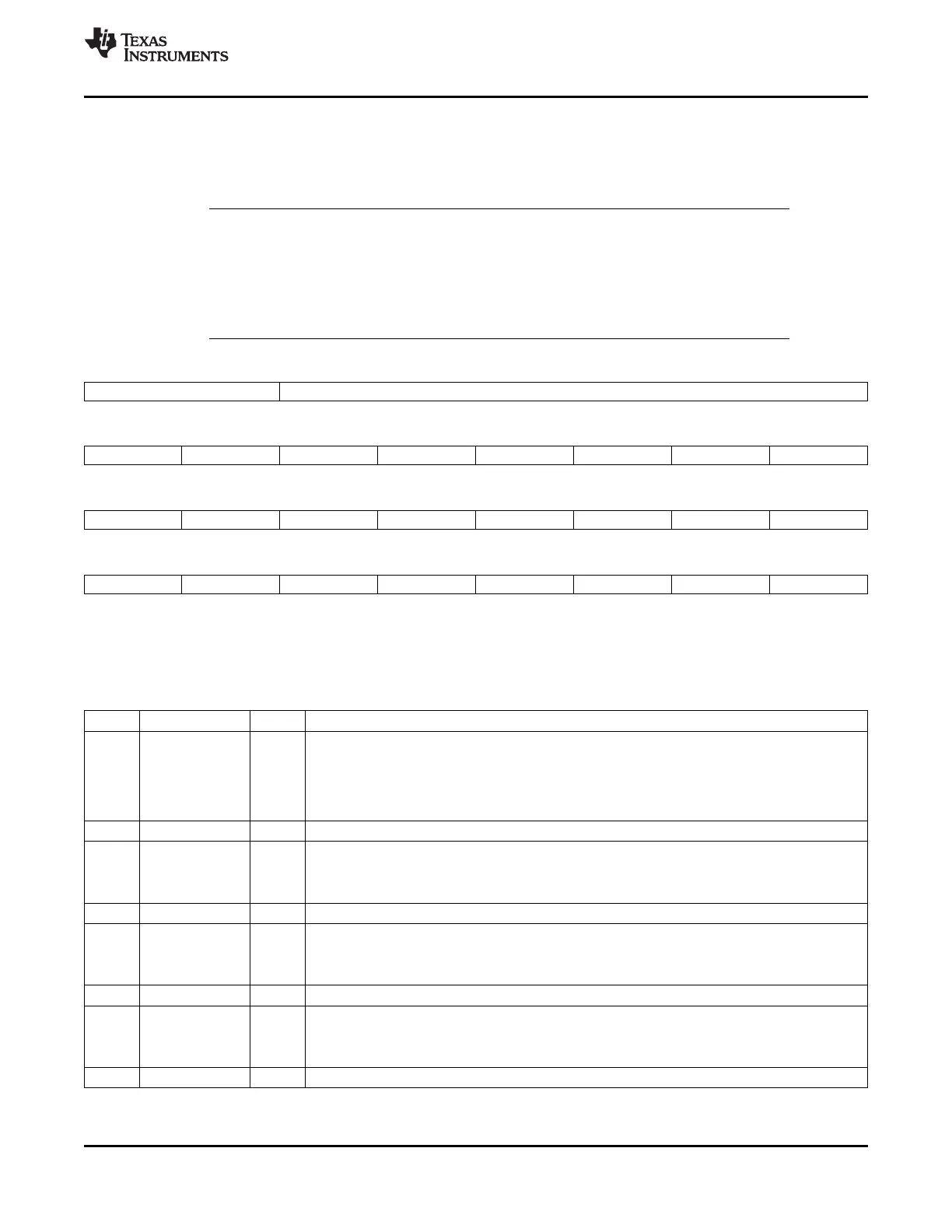

Table 3-7. Peripheral Configuration Register 0 (PERCFG0) Field Descriptions

Bit Field Value Description

31:30 SRIOCTL Mode control for SRIO. SRIO does not have a corresponding status bit in the Peripheral Status

Registers. Once SRIOCTL is set to 11b, the SRIO peripheral can be used within 16 SYSCLK3

cycles.

00b Set SRIO to disabled mode

11b Set SRIO to enabled mode

29:23 Reserved Reserved.

22 UTOPIACTL Mode control for UTOPIA

0 Set UTOPIA to disabled mode

1 Set UTOPIA to enabled mode

21 Reserved Reserved.

20 PCICTL Mode control for PCI. This bit defaults to 1 when host boot is used (BOOTMODE[3:0] = 0111b).

0 Set PCI to disabled mode

1 Set PCI to enabled mode

19 Reserved Reserved.

18 HPICTL Mode control for HPI. This bit defaults to 1 when host boot is used (BOOTMODE[3:0] = 0001b).

0 Set HPI to disabled mode

1 Set HPI to enabled mode

17 Reserved 1 Reserved.

Copyright © 2005–2012, Texas Instruments Incorporated Device Configuration 63

Submit Documentation Feedback

Product Folder Link(s): TMS320C6455

Loading...

Loading...