TMS320C6455

SPRS276M –MAY 2005–REVISED MARCH 2012

www.ti.com

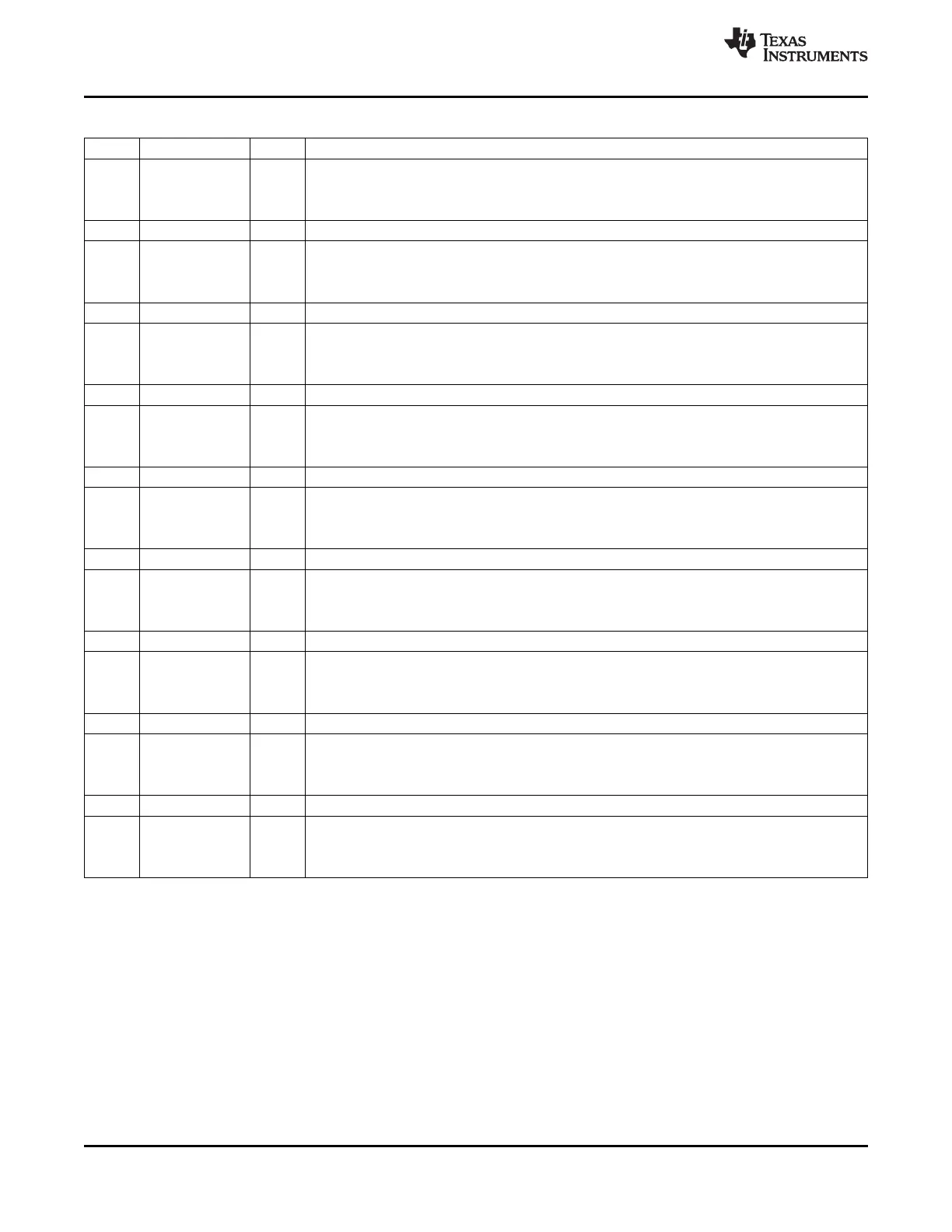

Table 3-7. Peripheral Configuration Register 0 (PERCFG0) Field Descriptions (continued)

Bit Field Value Description

16 McBSP1CTL Mode control for McBSP1

0 Set McBSP1 to disabled mode

1 Set McBSP1 to enabled mode

15 Reserved Reserved.

14 McBSP0CTL Mode control for McBSP0

0 Set McBSP0 to disabled mode

1 Set McBSP0 to enabled mode

13 Reserved Reserved.

12 I2CCTL Mode control for I2C

0 Set I2C to disabled mode

1 Set I2C to enabled mode

11 Reserved Reserved.

10 GPIOCTL Mode control for GPIO

0 Set GPIO to disabled mode

1 Set GPIO to enabled mode

9 Reserved Reserved.

8 TIMER1CTL Mode control for Timer 1

0 Set Timer 1 to disabled mode

1 Set Timer 1 to enabled mode

7 Reserved Reserved.

6 TIMER0CTL Mode control for Timer 0

0 Set Timer 0 to disabled mode

1 Set Timer 0 to enabled mode

5 Reserved Reserved.

4 EMACCTL Mode control for EMAC/MDIO

0 Set EMAC/MDIO to disabled mode

1 Set EMAC/MDIO to enabled mode

3 Reserved Reserved.

2 VCPCTL Mode control for VCP

0 Set VCP to disabled mode

1 Set VCP to enabled mode

1 Reserved Reserved.

0 TCPCTL Mode control for TCP

0 Set TCP to disabled mode

1 Set TCP to enabled mode

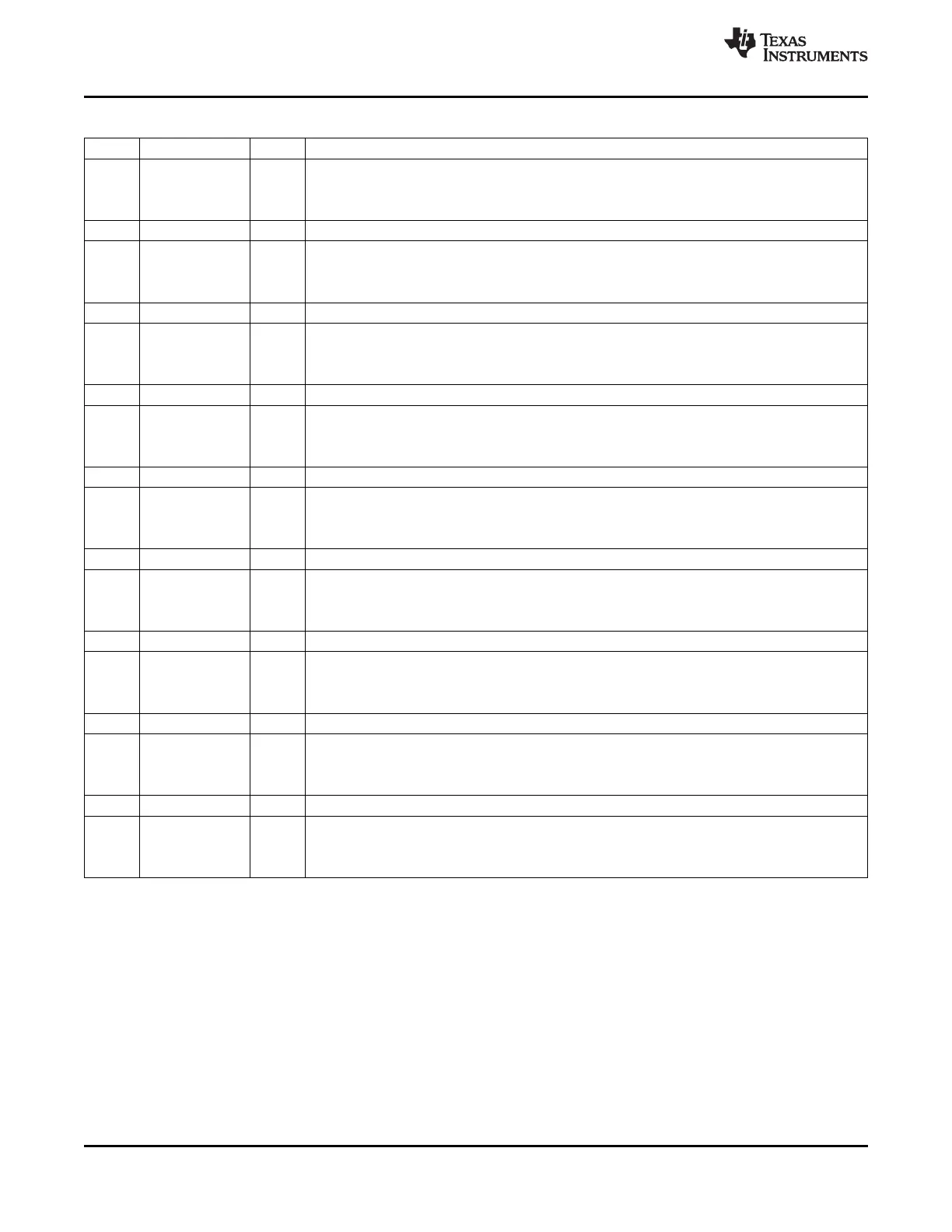

3.4.3 Peripheral Configuration Register 1 Description

The Peripheral Configuration Register (PERCFG1) is used to enable the EMIFA and DDR2 Memory

Controller. EMIFA and the DDR2 Memory Controller do not have corresponding status bits in the

Peripheral Status Registers. The EMIFA and DDR2 Memory Controller peripherals can be used within 16

SYSCLK3 cycles after EMIFACTL and DDR2CTL are set to 1. Once EMIFACTL and DDR2CTL are set to

1, they cannot be set to 0. Note that if the DDR2 Memory Controller and EMIFA are disabled at reset

through the device configuration pins (DDR2.EN[ABA0] and EMIFA[ABA1]), they cannot be enabled

through the PERCFG1 register.

64 Device Configuration Copyright © 2005–2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320C6455

Loading...

Loading...