Device Overview

MFR4310 Reference Manual, Rev. 2

36 Freescale Semiconductor

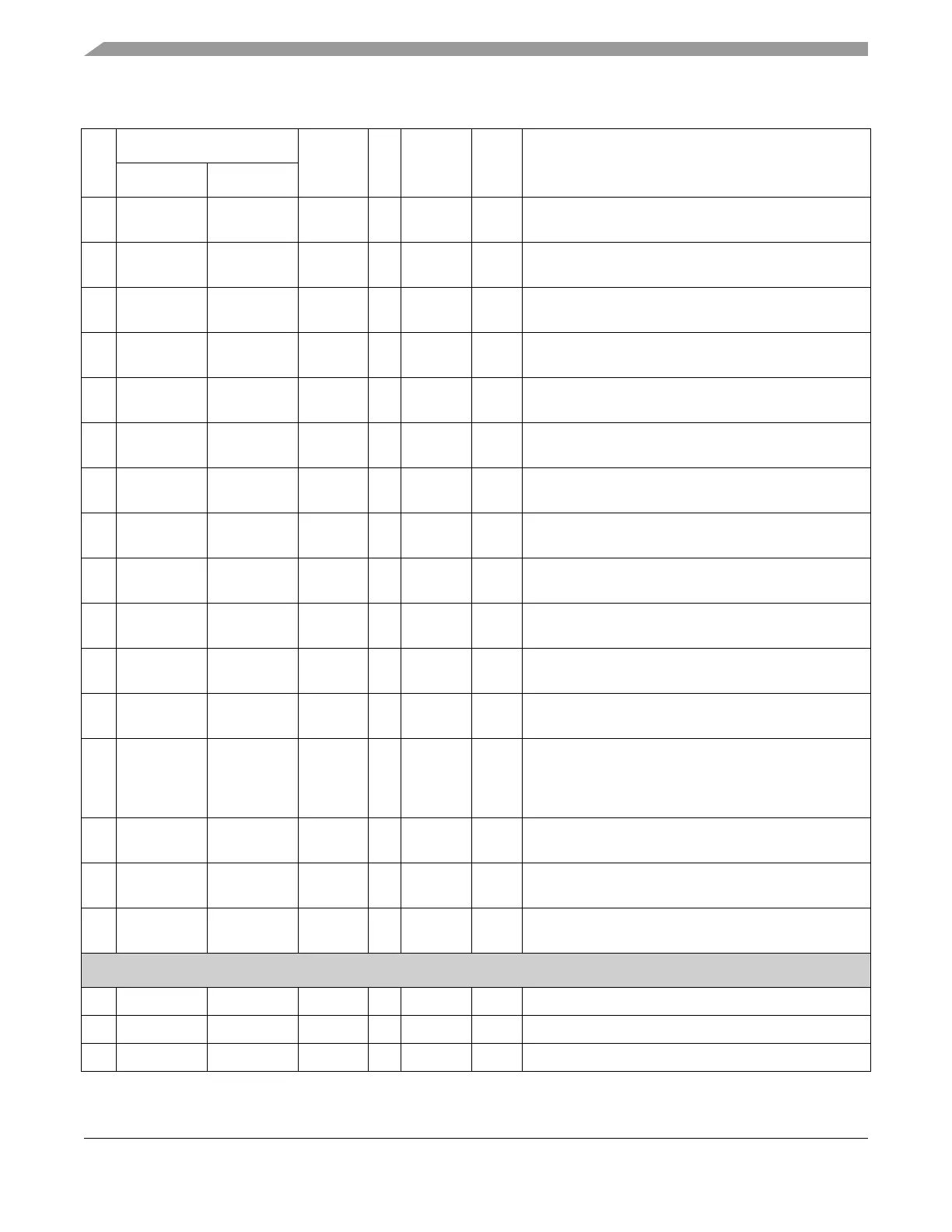

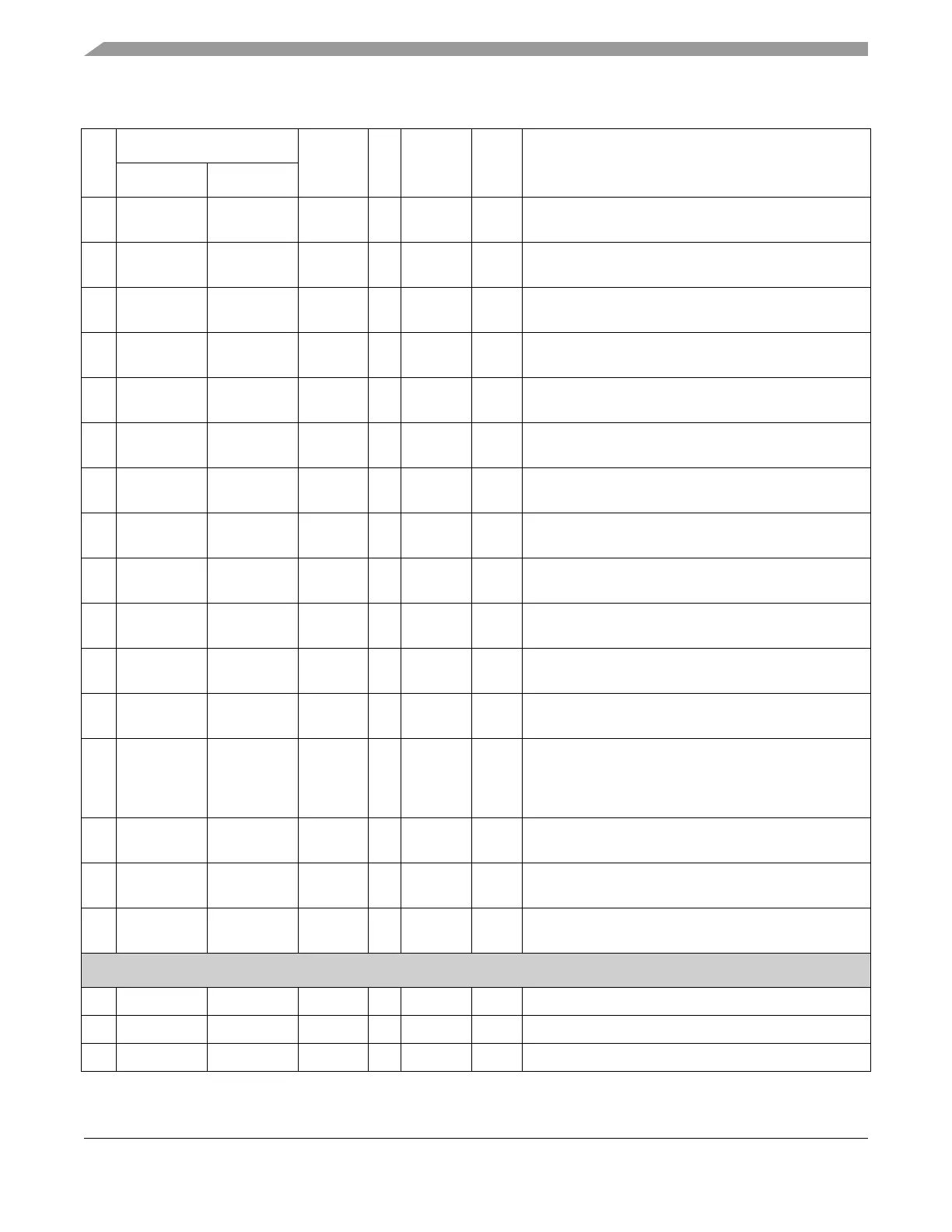

5 D12 PB3 VDDX I/O Z/DC/PC Z AMI/MPC data bus;

HCS12 multiplexed address/data bus

4 D11 PB4 VDDX I/O Z/DC/PC Z AMI/MPC data bus;

HCS12 multiplexed address/data bus

3 D10 PB5 VDDX I/O Z/DC/PC Z AMI/MPC data bus;

HCS12 multiplexed address/data bus

2 D9 PB6 VDDX I/O Z/DC/PC Z AMI/MPC data bus;

HCS12 multiplexed address/data bus

62 D8 PB7 VDDX I/O Z/DC/PC Z AMI/MPC data bus;

HCS12 multiplexed address/data bus

61 D7 PA0 VDDX I/O Z/DC/PC Z AMI/MPC data bus;

HCS12 multiplexed address/data bus

58 D6 PA1 VDDX I/O Z/DC/PC Z AMI/MPC data bus;

HCS12 multiplexed address/data bus

57 D5 PA2 VDDX I/O Z/DC/PC Z AMI/MPC data bus;

HCS12 multiplexed address/data bus

56 D4 PA3 VDDX I/O Z/DC/PC Z AMI/MPC data bus;

HCS12 multiplexed address/data bus

55 D3 PA4 VDDX I/O Z/DC/PC Z AMI/MPC data bus;

HCS12 multiplexed address/data bus

51 D2 PA5 VDDX I/O Z/DC/PC Z AMI/MPC data bus;

HCS12 multiplexed address/data bus

40 D1 PA6 VDDX I/O Z/DC/PC Z AMI/MPC data bus;

HCS12 multiplexed address/data bus

39 D0 PA7 VDDX I/O Z/DC/PC Z AMI/MPC data bus;

HCS12 multiplexed address/data bus.

D0 is the LSB of the AMI data bus; PA7 is the MSB of

the HCS12 address/data bus

29 CE# LSTRB VDDX I PC - AMI/MPC chip select signal;

HCS12 low-byte strobe signal

30 WE# RW_CC# VDDX I PC - AMI write enable signal;

HCS12 read/write select signal

52 A10 ECLK_CC VDDX I PC - AMI/MPC address bus;

HCS12 clock input

Physical Layer Interface

33 RXD_BG1 - VDDX I PC - PHY Data receiver input

43 RXD_BG2 - VDDX I PC - PHY Data receiver input

36 TXEN1# - VDDX O DC 1 Transmit enable for PHY

Table 2-3. Pin Functions and Signal Properties (continued)

Pin

#

Pin Name

1

Powered

by

I/O

Pin

Type

2, 3

Reset Functional Description

Function 1 Function 2

Loading...

Loading...