boards.fm

A31003-H3590-S100-7-7620, 06/2012

HiPath 3000/5000 V9, Service documentation

3-93

Nur für den internen Gebrauch Boards for HiPath 3000

Peripheral boards

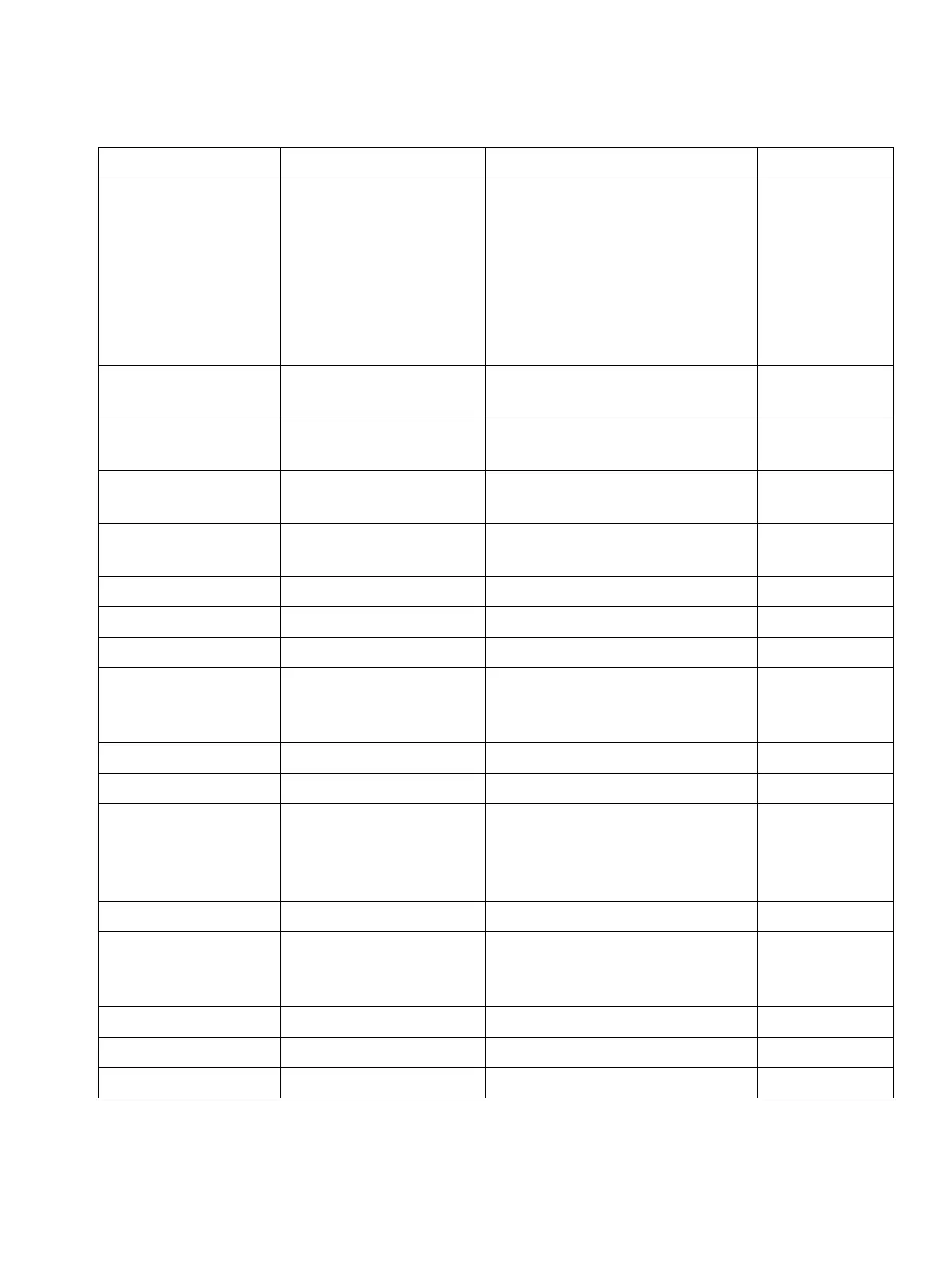

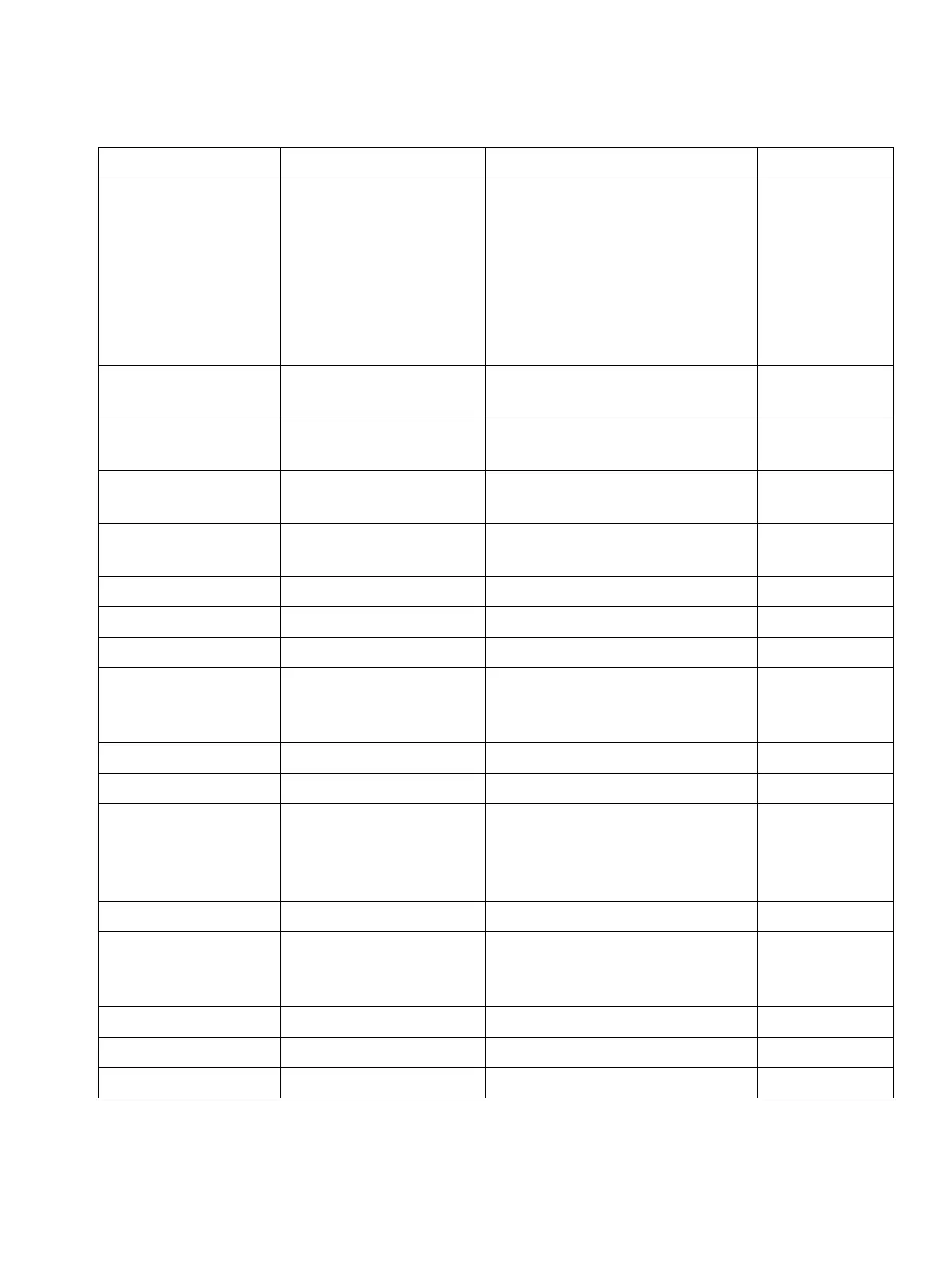

BGx_0A,

BGx_0B

X1-02, X1-26

X1-06, X1-08

X1-10, X2-02

X2-04, X2-06

X2-08, X2-10

X3-02, X3-04

X3-06, X3-08

X3-10, X4-02

Sets 0 to 7 AB pair Not connected

HO0 … HO3 X8-22, X7-30, X8-44,

X8-42

Old PCM lines (2.048 Mbps) Input

HI0 … HI3 X9-24, X9-02, X9-44,

X9-42

Old PCM lines (2.048 Mbps) Output

WHO0 … WHO3 X6-32, X6-33, X6-34,

X6-35

New PCM lines (2.048 Mbps) Input

WHI0 … WHI3 X7-31, X7-32, X7-33,

X7-34

New PCM lines (2.048 Mbps) Output

HDI X9-06 HDLC lines Input

HDO X8-04 HDLC lines Output

PRS X7-26 System reset Input

BA0 … BA6 X7-06, X7-28, X8-26

X8-28, X9-04, X8-06,

X8-2

Frame address recognition Input

FMB X9-22 Clock synchronization signal Input

CKA X8-08 System clock (2.048 MHz) Input

(CLS) X8-10 Clock selection

(CLS=GND --> CKA=2.048 MHz)

The (CLS) pin should be

earthed on the backplane.

Input

RCLK X7-02 Reference clock Output

RAC X7-04 Reference clock activation

Low-active for activating RCLK

Tristate for deactivating CLK

Output tristate

LWLOOP X4-04 Output for result of self-check Not connected

TOUT X6-48 Output for result of self-check Not connected

TCK X7-44 Boundary scan: check clock Not connected

Signal Name Connector contact Signal description Direction

Table 3-36 SIPAC Connector Contact Assignment

Loading...

Loading...