4

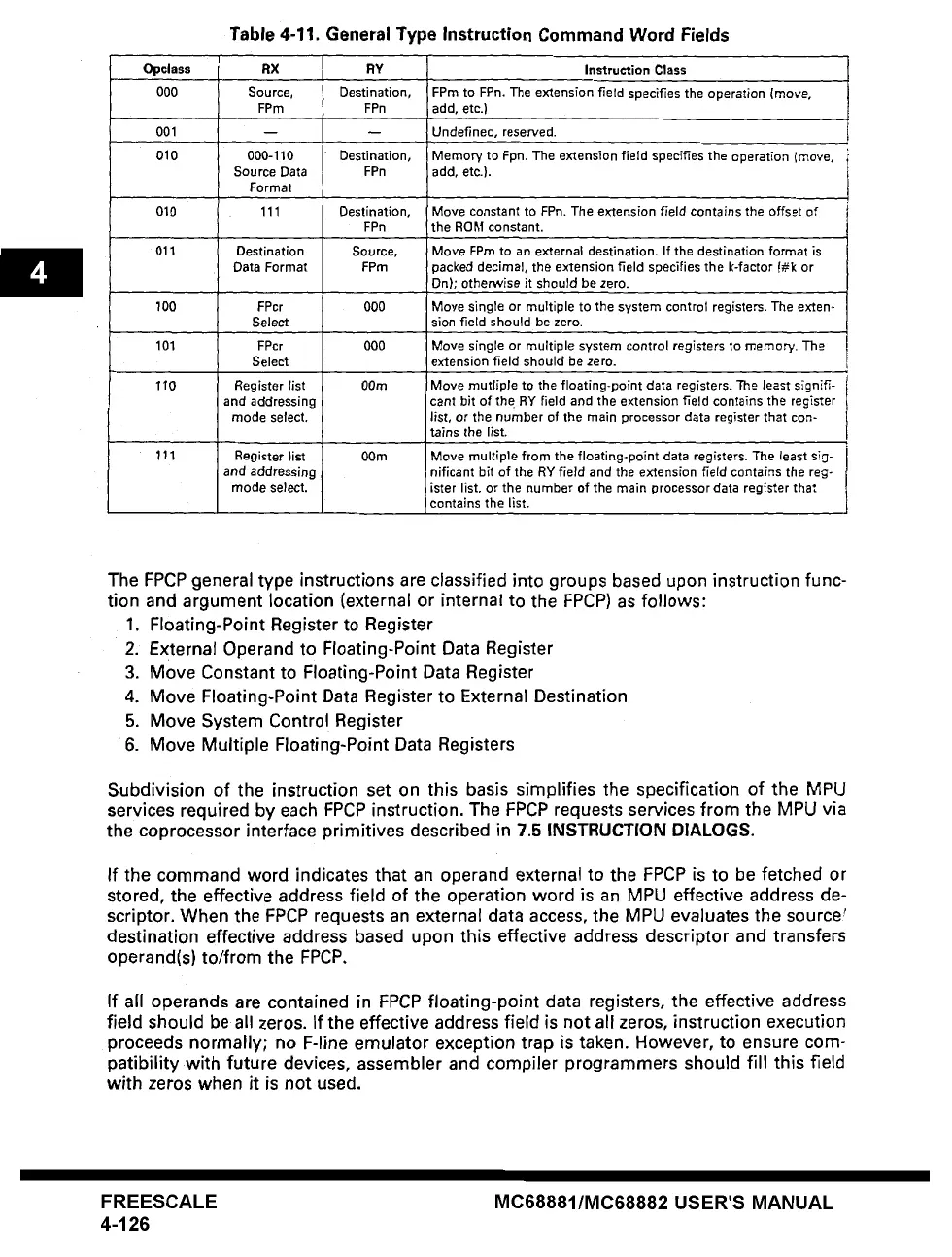

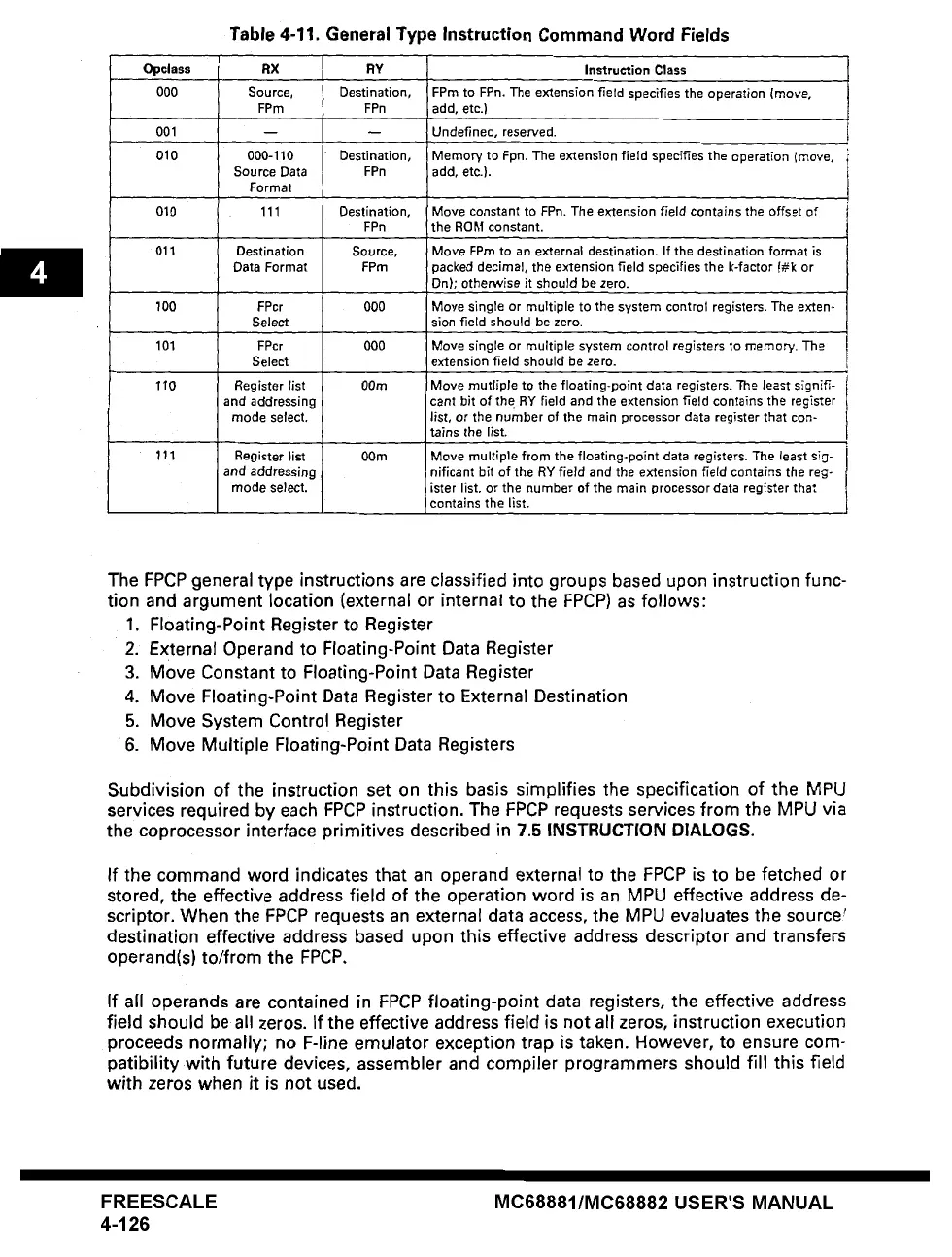

Table 4-11. General Type Instruction Command Word Fields

Opclass RX RY Instruction Class

000 Source, Destination, FPm to FPn. The extension field specifies the operation (move,

FPm FPn add, etc.)

001 -- -- Undefined, reserved.

010 000-110 Destination, Memory to Fpn. The extension field specifies the operation (move,

Source Data FPn add, etc.}.

Format

010 111 Destination, Move constant to FPn. The extension field contains the offset of

FPn the ROM constant.

011 Destination Source, Move FPm to an external destination. If the destination format is

Data Format FPm ~acked decimal, the extension field specifies the k-factor (#k or

Dn); otherwise it should be zero.

100 FPcr 000 Move single or multiple to the system control registers. The extem

Select sion field should be zero.

101 FPcr 000 Move single or multiple system control registers to memory. The

Select extension field should be zero.

110 Register list 00m Move mutliple to the floating-point data registers. The least signifi-

and addressing ~ cant bit of thff RY field and the extension field contains the register

mode select, list, or the number of the main processor data register that con-

tains the list.

111 Register list 00m Move multiple from the floating-point data registers. The least sig-

and addressing nifieant bit of the RY field and the extension field contains the rag-

mode select. , Lster list, or the number of the main processor data register that

I contains the list.

The FPCP general type instructions are classified into groups based upon instruction func-

tion and argument location (external or internal to the FPCP) as follows:

1. Floating-Point Register to Register

2. External Operand to Floating-Point Data Register

3. Move Constant to Floating-Point

Data

Register

4. Move Floating-Point Data Register to External Destination

5. Move System Control Register

6. Move Multiple Floating-Point Data Registers

Subdivision of the instruction set on this basis simplifies the specification of the MPU

services required by each FPCP instruction. The FPCP requests services from the MPU via

the coprocessor interface primitives described in 7.5 INSTRUCTION DIALOGS.

If the command word indicates that an operand external to the FPCP is to be fetched or

stored, the effective address field of the operation word is an MPU effective address de-

scriptor. When the FPCP requests an external data access, the MPU evaluates the source ~

destination effective address based upon this effective address descriptor and transfers

operand(s) to/from the FPCP,

If all operands are contained in FPCP floating-point data registers, the effective address

field should beall zeros. If the effective address field is not all zeros, instruction execution

proceeds normally; no F-line emulator exception trap is taken. However, to ensure com-

patibility with future devices, assembler and compiler programmers should fill this field

with zeros when it is not used.

FREESCALE

4-126

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...