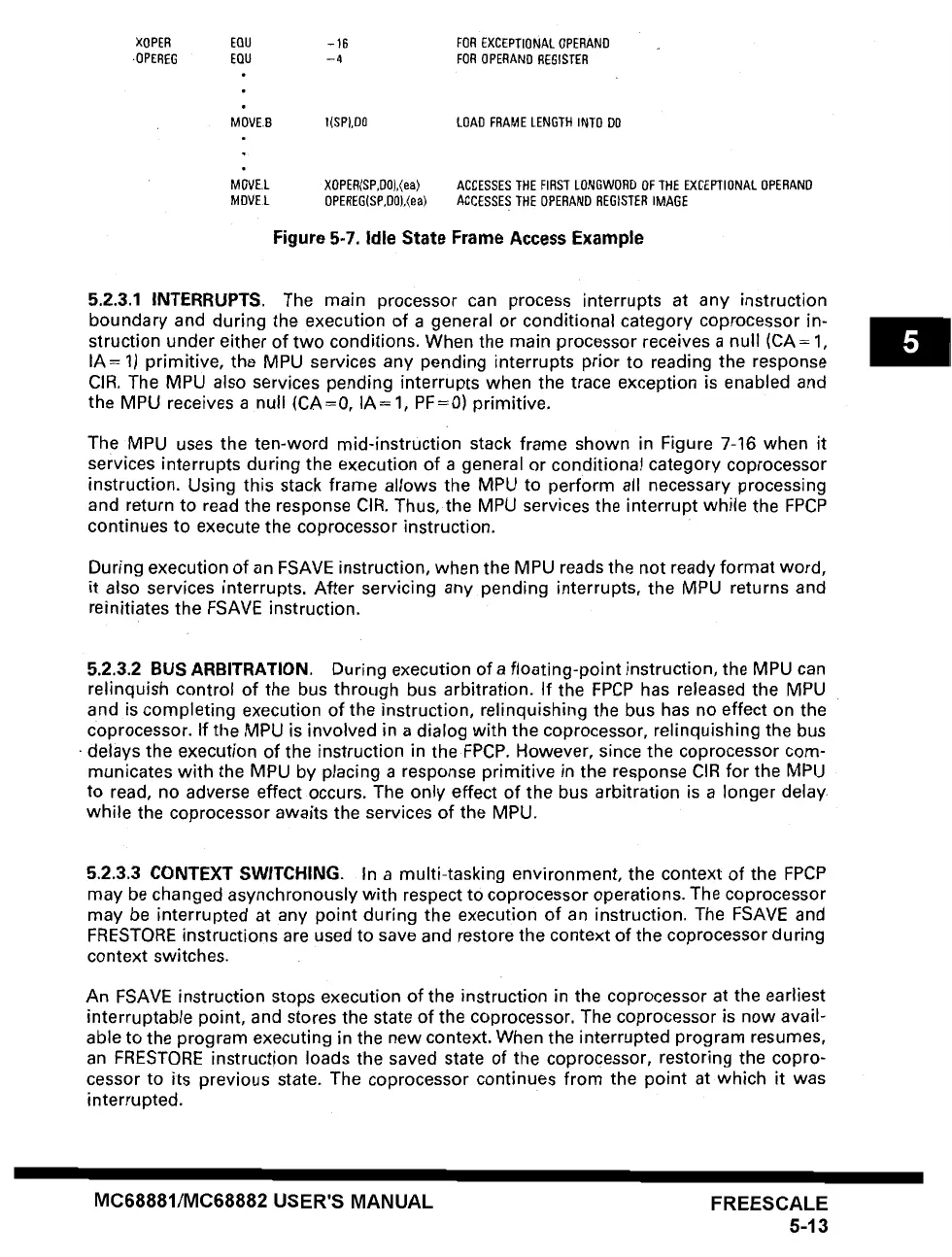

XOPER EQU - 16 FOR EXCEPTIONAL OPERAND

• OPEREG EQU -4 FOR OPERAND REGISTER

MOVE.B I(SP),O0 LOAD FRAME LENGTH INTO DO

MOVE.L XOPER(SP,GO),<ea) ACCESSES "[HE FIRST LONGWORD OF THE EXCEPTIONAL OPERAND

MOVEi OPEREG(SP,DO),<ea) ACCESSES THE OPERAND REGISTER IMAGE

Figure 5-7. Idle State Frame Access Example

5.2.3.1 INTERRUPTS. The main processor can process interrupts at any instruction

boundary and during the execution of a general or conditional category coprocessor in-

struction under either of two conditions. When the main processor receives a null (CA = 1,

IA= 1) primitive, the MPU services any pending interrupts prior to reading the response

CIR. The MPU also services pending interrupts when the trace exception is enabled and

the MPU receives a null (CA=O, IA= 1, PF=O) primitive.

The MPU uses the ten-word mid-instruction stack frame shown in Figure 7-16 when it

services interrupts during the execution of a general or conditional category coprocessor

instruction. Using this stack frame allows the MPU to perform all necessary processing

and return to read the response CIR. Thus, the MPU services the interrupt while the FPCP

continues to execute the coprocessor instruction.

During execution of an FSAVE instruction, when the MPU reads the not ready format word,

it also services interrupts. After servicing any pending interrupts, the MPU returns and

reinitiates the FSAVE instruction.

5.2.3.2 BUS ARBITRATION. During execution of a floating-point instruction, the MPU can

relinquish control of the bus through bus arbitration. If the FPCP has released the MPU

and is completing execution of the instruction, relinquishing the bus has no effect on the

coprocessor. If the MPU is involved in a dialog with the coprocessor, relinquishing the bus

• delays the execution of the instruction in the FPCP. However, since the coprocessor com-

municates with the MPU by placing a response primitive in the response CIR for the MPU

to read, no adverse effect occurs. The only effect of the bus arbitration is a longer delay

while the coprocessor awaits the services of the MPU.

5.2.3.3 CONTEXT SWITCHING. In a multi-tasking environment, the context of the FPCP

may be changed asynchronously with respect to coprocessor operations. The coprocessor

may be interrupted at any point during the execution of an instruction. The FSAVE and

FRESTORE instructions are used to save and restore the context of the coprocessor during

context switches.

An FSAVE instruction stops execution of the instruction in the coprocessor at the earliest

interruptable point, and stores the state of the coprocessor. The coprocessor is now avail-

able to the program executing in the new context. When the interrupted program resumes,

an FRESTORE instruction loads the saved state of the coprocessor, restoring the copro-

cessor to its previous state. The coprocessor continues from the point at which it was

interrupted.

MC68881/MC68882 USER'S MANUAL FREESCALE

5-13

Loading...

Loading...