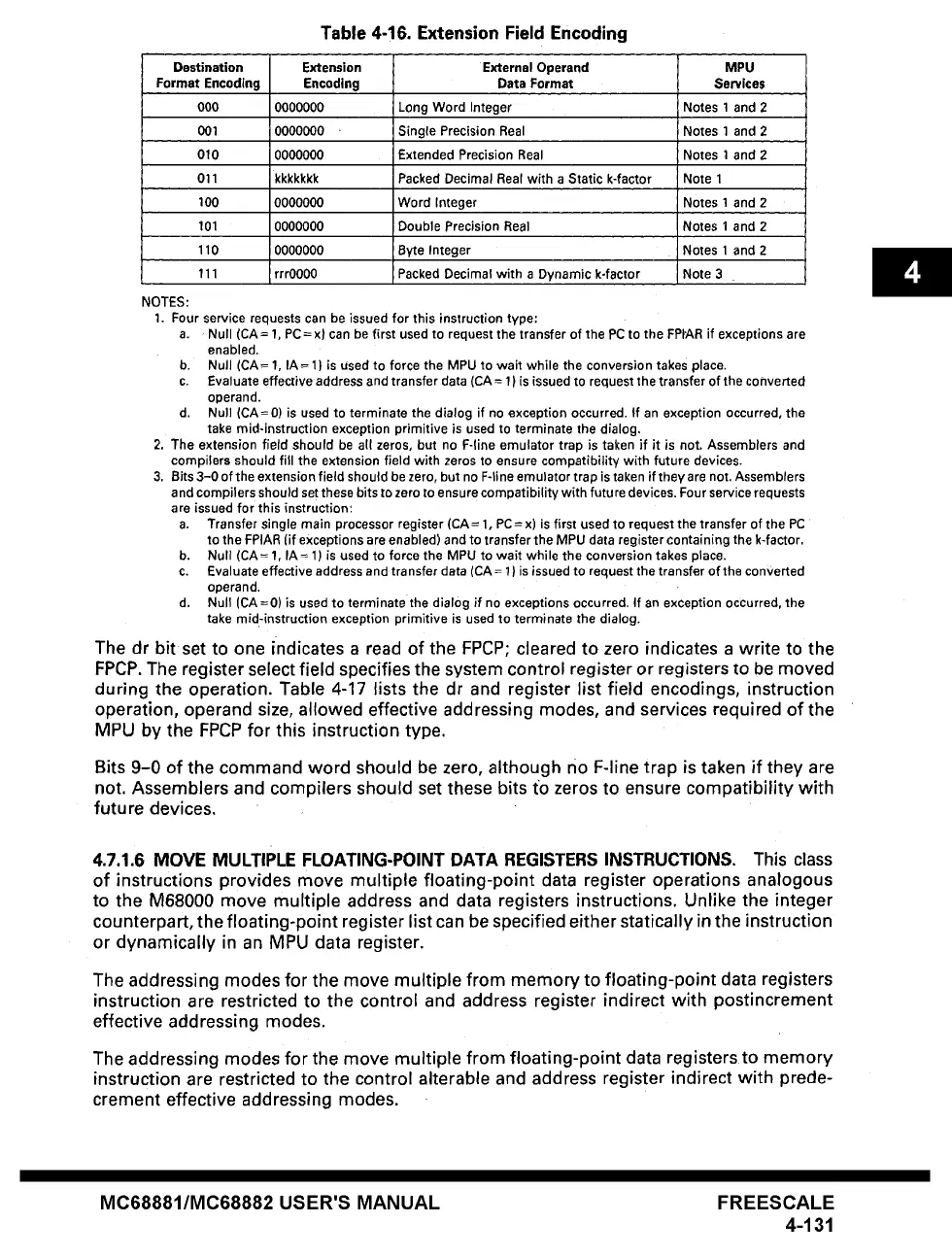

Table 4-16. Extension Field Encoding

Destination Extension External Operand MPU

Format Encoding Encoding Data Format Services

000 0O00000 Long Word Integer Notes 1 and 2

001 0000000 • Single Precision Real Notes 1 and 2

010 0000000 Extended Precision Real Notes 1 and 2

011 kkkkkkk Packed Decimal Real with a Static k-factor Note 1

100 0000000 Word Integer Notes 1 and 2

101 0000000 Double Precision Real Notes 1 and 2

110 0000000 Byte Integer Notes I and 2

111 rrr0O00 Packed Decimal with a Dynamic k-factor Note 3

NOTES:

1. Four service requests can be issued for this instruction

type:

a. Null (CA= 1, PC=x) can be first used to request the transfer of the PC to the FPI~R if exceptions are

enabled.

b. Null (CA= 1, IA= 1) is used to force the MPU to wait while the conversion takes place.

c. Evaluate effective address and transfer data (CA = 1 ) is issued to request the transfer of the converted

operand.

d. Null (CA = 0) is used to terminate the dialog if no exception occurred. If an exception occurred, the

take mid-instruction exception primitive is used to terminate the dialog,

2. The extension field should be all zeros, but no F-line emulator trap is taken if it is not. Assemblers and

compilers should fill the extension field with zeros to ensure compatibility with future devices.

3. Bits 3-0 of the extension field should be zero, but no F-line emulator trap is taken if they are not. Assemblers

and compiler s should se t these bits to zero to ensure compatibility with futu re devices. Four service requests

are

issued for this instruction:

a. Transfer single main processor register (CA= 1, PC = x) is first used to request the transfer of the PC

to the FPIAR (if exceptions are enabled) and to transfer the MPU data register containing the k-factor.

b. Null (CA = 1, IA = 1) is used to force the MPU to wait while the conversion takes place.

c. Evaluate effective address and transfer

data

(CA = 1 ) is issued to request the transfer of the converted

operand.

d. Null (CA=0) is used to terminate the dialog if no exceptions occurred. If an exception occurred, the

take mid-instruction exception primitive is used to terminate the dialog.

The dr bit set to one indicates a read of the FPCP; cleared to zero indicates a write to the

FPCP. The register select field specifies the system control register or registers to be moved

during the operation. Table 4-17 lists the dr and register list field encodings, instruction

operation, operand size, allowed effective addressing modes, and services required of the

MPU by the FPCP for this instruction type.

Bits 9-0 of the command word should be zero, although no F-line trap is taken if they are

not. Assemblers and compilers should set these bits to zeros to ensure compatibility with

future devices,

4.7.1.6 MOVE MULTIPLE FLOATING-POINT DATA REGISTERS INSTRUCTIONS. This class

of instructions provides move multiple floating-point data register operations analogous

to the M68000 move multiple address and data registers instructions. Unlike the integer

counterpart, the floating-point register list can be specified either statically in the instruction

or dynamically in an MPU data register.

The addressing modes for the move multiple from memory to floating-point data registers

instruction are restricted to the control and address register indirect with postincrement

effective addressing modes.

The addressing modes for the move multiple from floating-point data registers to memory

instruction are restricted to the control alterable and address register indirect with prede-

crement effective addressing modes.

MC66661/MC66662 USER'S MANUAL FREESCALE

4-131

Loading...

Loading...