4

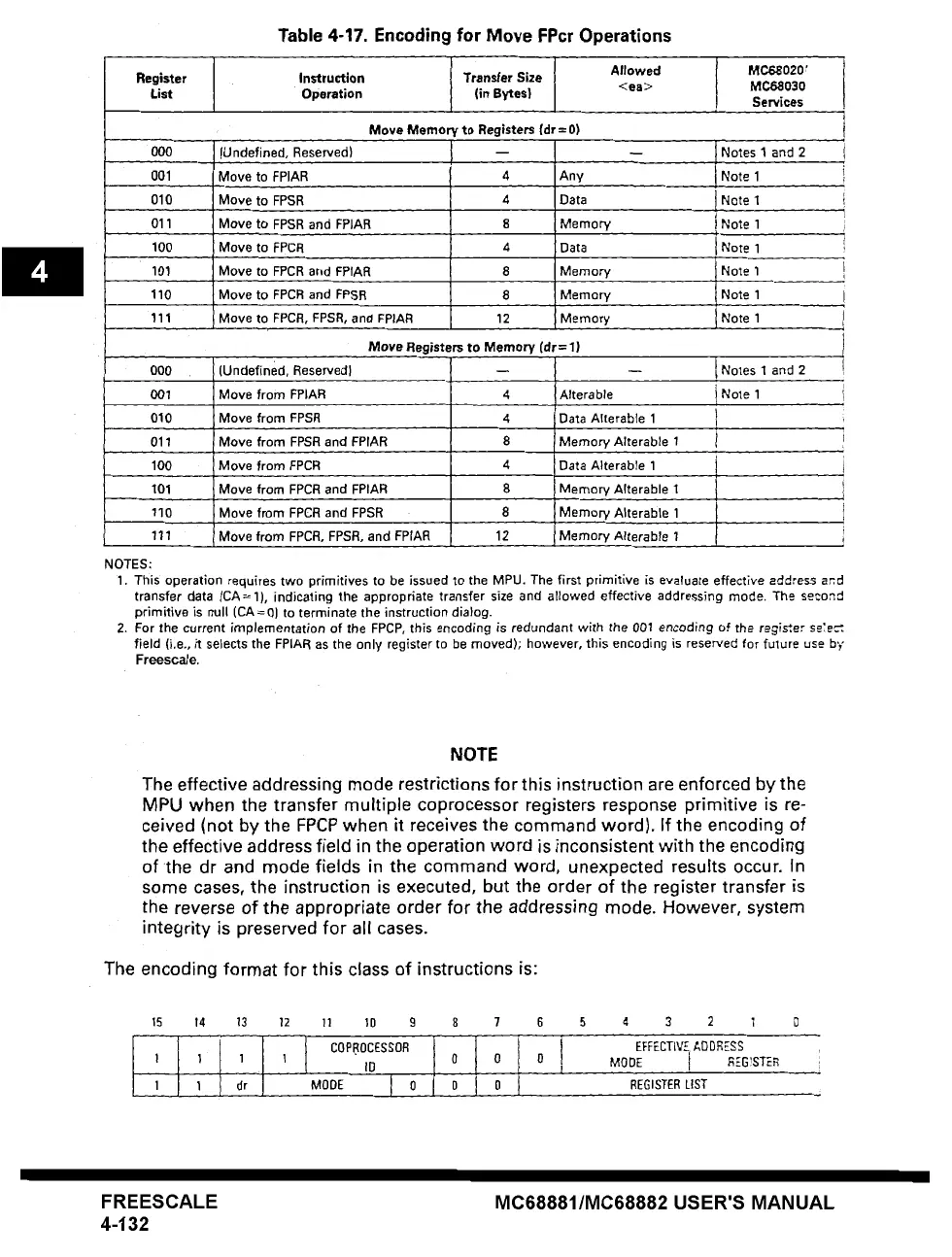

Table 4-17. Encoding for Move FPcr Operations

Register Instruction I Transfer Size I Allowed MC680Z0,'

List Operation (in Bytes) <ea> MC68030

Services

Move Memor to Registers [dr=O)

000 (Undefined, Reserved) -- -- Notes 1 and 2

001 Move to FPIAR 4 Any Note 1

010 Move to FPSR 4 Data ! Note 1

011 Move to FPSR and FPIAR 8 Memory 1 Note 1

)

100 Move to FPCR 4 Data l Note 1

101 Move to FPCR and FPIAR 8 Memory .Note 1

110 Move to FPCR and FPSR 8 Memory Note 1

111 Move to FPCR, FPSR, and FPIAR 12 Memory 1 Note 1

000

Move Registers to Memory (dr

= 1)

(Undefined, Reserved}

INgles 1 and 2

NOTES:

i Note 1 001 Move from FPIAR 4 Alterable

010 Move from FPSR 4 Data Alterable 1 1 i

011 Move from FPSR and FPIAR 8 Memory Alterable 1 i

., 1

100 Move from FPCR 4 Data Alterable 1 j

I

101 Move from FPCR and FPIAR 8 Memory Alterable 1

110 Move from FPCR and FPSR 8 Memory Alterable 1

12

Memory

Atterabb 1

111 Move from FPCR, FPSR, and FPIAR

1. This operation requires two primitives to be issued to the MPU. The first primitive is evaluate effective address a~d

transfer data [CA= 1), indicating the appropriate transfer size and allowed effective addressing mode. The second

primitive is null (CA=0) to terminate the instruction dialog.

2. For the current

implementation

of the FPCP, this encoding is redundant with

the

001

encoding

of the

regi~er se~e~

field (i.e,, it selects the FPIAR as the only register to be moved); however, this encoding is reserved for future use by

Freescale.

NOTE

The effective addressing mode restrictions for this instruction are enforced by the

MPU when the transfer multiple coprocessor registers response primitive is re-

ceived (not by the FPCP when it receives the command word). If the encoding of

the effective address field in the operation word is inconsistent with the encoding

of the dr and mode fields in the command word, unexpected results occur. In

some cases, the instruction is executed, but the order of the register transfer is

the reverse of the appropriate order for the

addressing

mode. However, system

integrity is preserved for all cases.

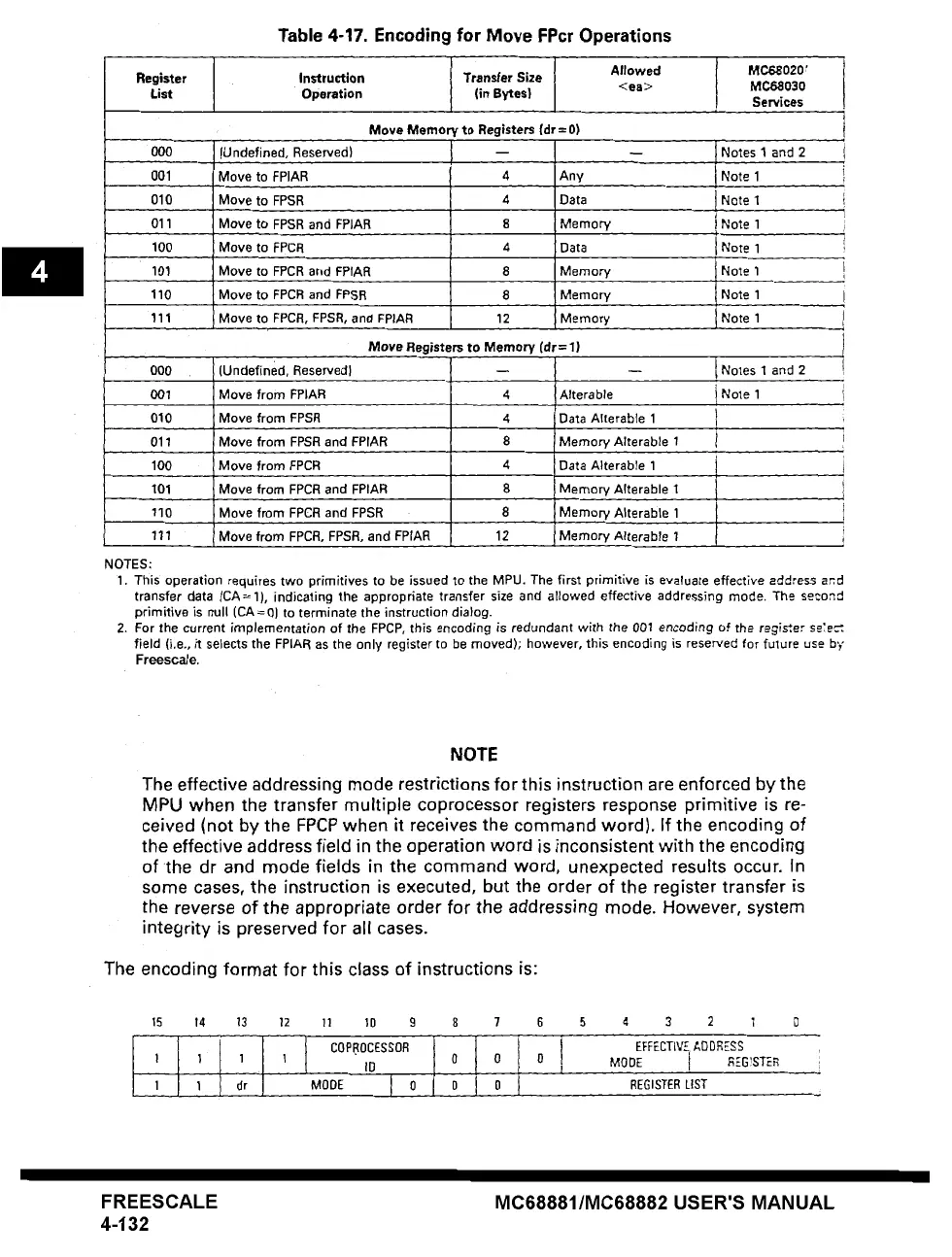

The encoding format for this class of instructions is:

15 14 13 12 11 11) 9 8 "/ 6 5 4 3 2 1 0

1 1 1 1 IO 0 0 0 i MODE l 8EG!STER

I

I I dr J 0 J

FREESCALE

4-132

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...