4

makes a request for a

transferto

an external destination, the length (in bytes) of the operand,

and the allowed effective addressing modes are specified in the primitive.

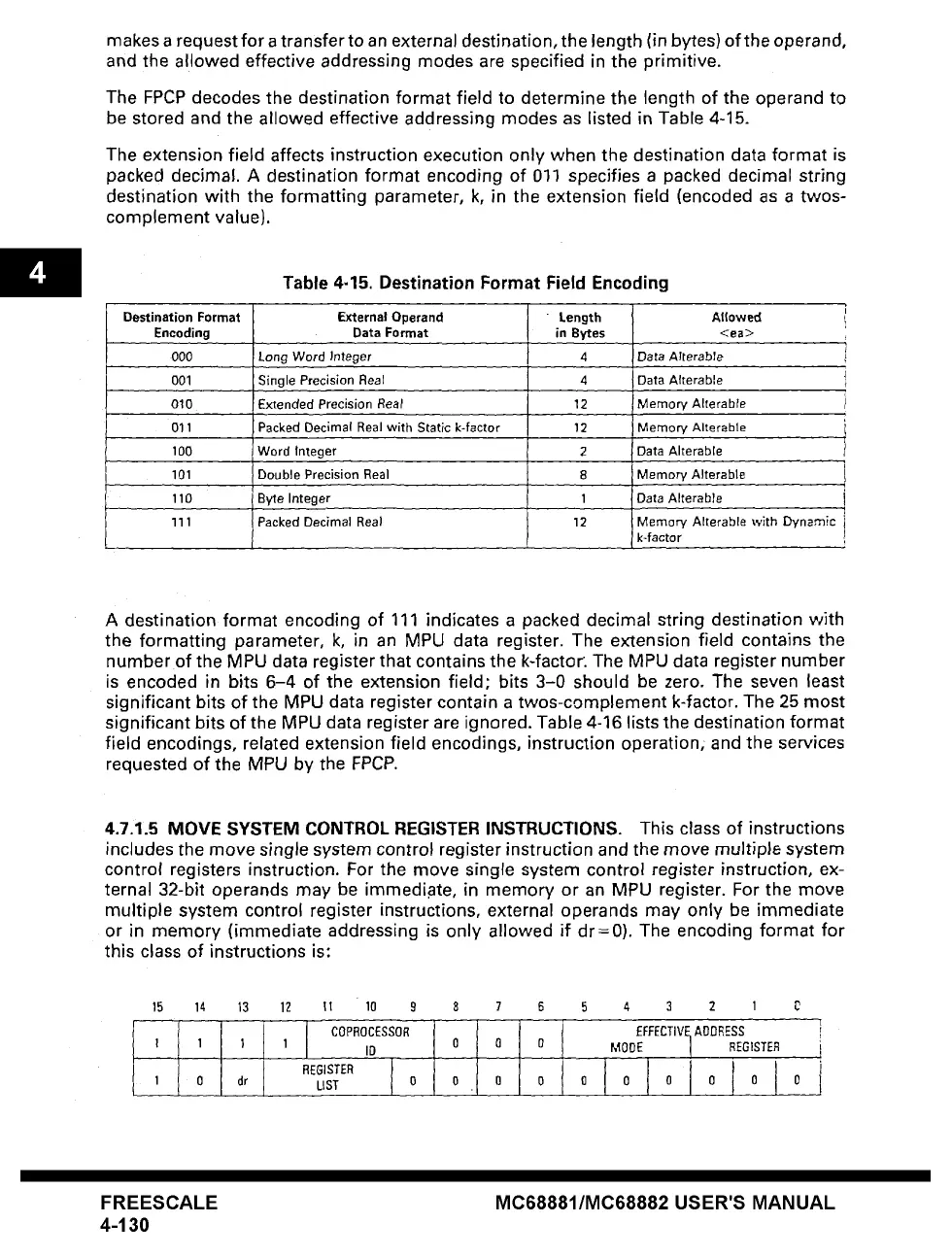

The FPCP decodes the destination format field to determine the length of the operand to

be stored and the allowed effective addressing modes as listed in Table 4-15.

The extension field affects instruction execution only when the destination data format is

packed decimal. A destination format encoding of 011 specifies a packed decimal string

destination with the formatting parameter, k, in the extension field (encoded as a twos-

complement value).

Table 4-15. Destination Format Field Encoding

Destination Format

Encoding

000

001

010

Oll

100

101

External Operand

Data Format

Long

Word Jnteger

Single Precision

Real

Extended Precision Beat

Packed Decimal Real with Static k-factor

Word Integer

Double Precision Real

Length A|(owed

in Bytes

<ea>

4 Data

AIterabte

4 Data Alterabte

12

12

Memory Alterabte

Memory Alterable

Data Alterable

Memory AIterabte

110

Byte Integer 1 Data Alterable

111

Packed Decimal

Real

12 Memory Alterable with Dynamic

k-factor

A destination format encoding of 111 indicates a packed decimal string destination with

the formatting parameter, k, in an MPU data register. The extension field contains the

number of the MPU data register that contains the k-factor. The MPU data register number

is encoded in bits 6-4 of the extension field; bits 3-0 should be zero. The seven least

significant bits of the MPU data register contain a twos-complement k-factor. The 25 most

significant bits of the MPU data register are ignored. Table 4-16 lists the destination format

field encodings, related extension field encodings, instruction operation; and the services

requested of the MPU by the FPCP.

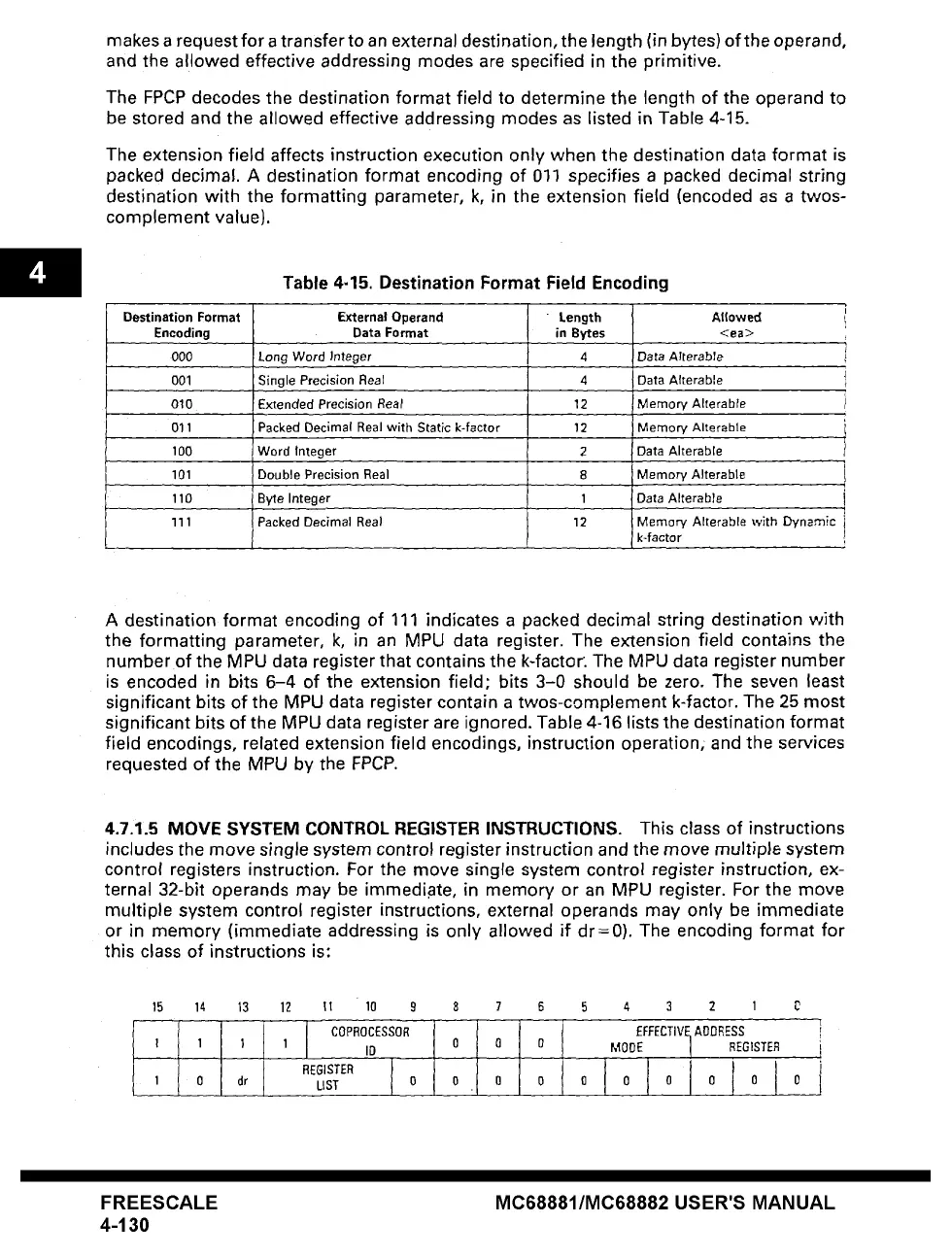

4.7.1.5 MOVE SYSTEM CONTROL REGISTER INSTRUCTIONS. This class of instructions

includes the move single system control register instruction and the move multiple system

control registers instruction. For the move single system control

register

instruction,

ex-

ternal 32-bit operands may be immedi.ate, in memory or an MPU register. For the move

multiple system control register instructions, external operands may only be immediate

or in memory (immediate addressing is only allowed if dr=0). The encoding format for

this class of instructions is:

15 14 13

! 1 1

1 0 dr

12 II 10 9 8 7 6 5 4 3 2 1

I '

COPROCESSOR EFFECTIVF] ADDRESS f

I ID 0 0 0 MODE ~ REGISTER i

UST 0 0 O 0 0 0 0 0 0 0

FREESCALE

4-130

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...