4

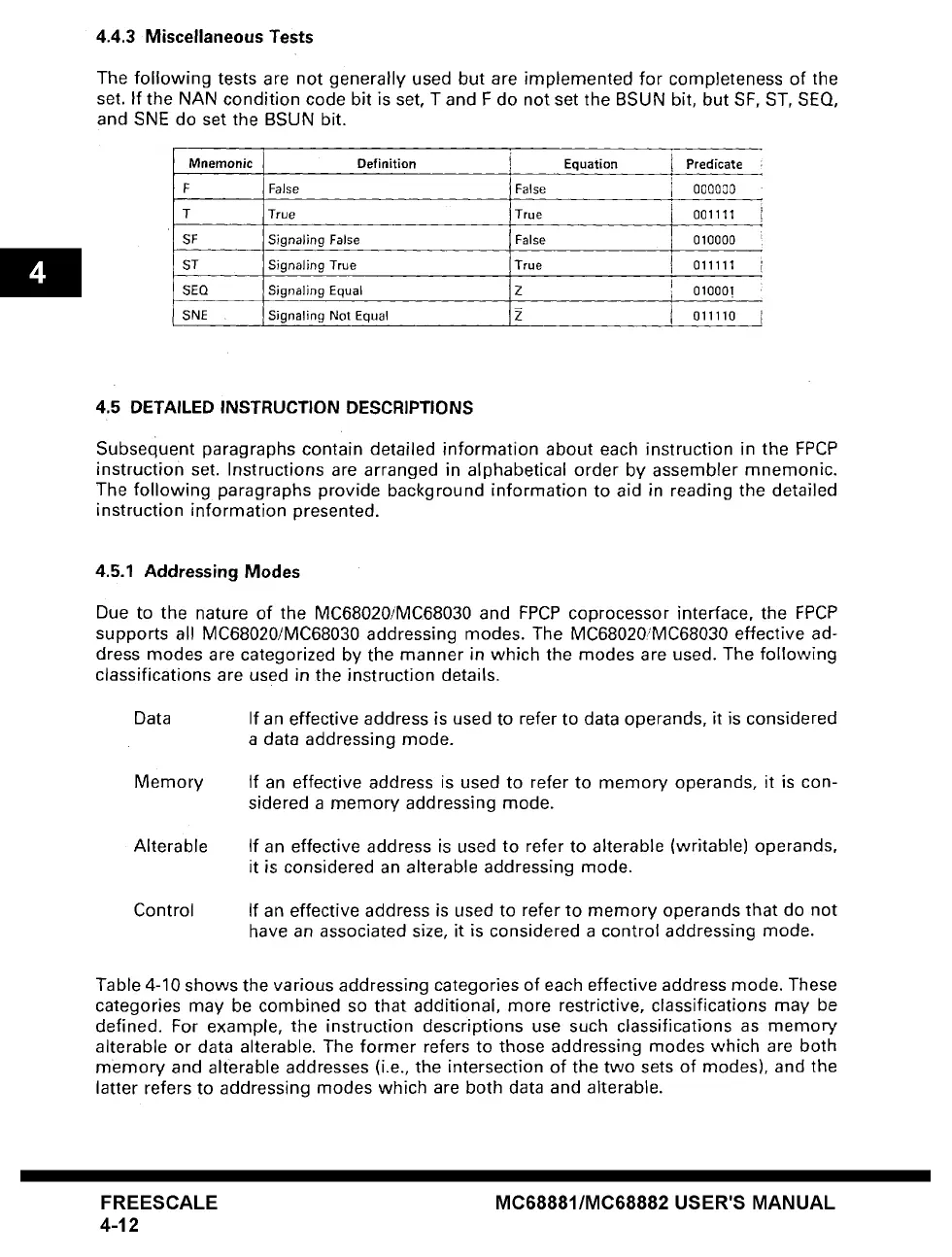

4.4.3 Miscellaneous Tests

The following tests are not generally used but are implemented for

set. If the NAN condition code bit is set, T and F do not set the BSUN

and SNE do set the BSUN bit.

completeness of the

bit, but SF, ST, SEQ,

Mnemonic

SF

Definition

i

I

False

True

Signaling False

False

True

False

Equation

i Predicate

i 0000O0

i

001111

t 010000

011111 ST Signaling True True

SEQ Signaling Equal Z i 010007

SNE Signaling Not Equal Z i 011110

4.5 DETAILED INSTRUCTION DESCRIPTIONS

Subsequent paragraphs contain detailed information about each instruction in the FPCP

instruction set. Instructions are arranged in alphabetical order by assembler mnemonic.

The following paragraphs provide background information to aid in reading the detailed

instruction information presented.

4.5.1 Addressing Modes

Due to the nature of the MC68020/MC68030 and FPCP coprocessor interface, the FPCP

supports all MC6802O/MC68030 addressing modes. The MC68020MC68030 effective ad-

dress modes are categorized by the manner in which the modes are used. The following

classifications are used in the instruction details.

Data If an effective address is used to refer to data operands, it is considered

a data addressing mode.

Memory If an effective address is used to refer to memory operands, it is con-

sidered a memory addressing mode.

Alterable If an effective address is used to refer to alterable (writable) operands,

it is considered an alterable addressing mode.

Control If an effective address is used to refer to memory operands that do not

have an associated size, it is considered a control addressing mode.

Table 4-10 shows the various addressing categories of each effective address mode. These

categories may be combined so that additional, more restrictive, classifications may be

defined. For example, the instruction descriptions use such classifications as memory

alterable or data alterable. The former refers to those addressing modes which are both

memory and alterable addresses (i.e., the intersection of the two sets of modes), and the

latter refers to addressing modes which are both data and alterable.

FREESCALE

4-12

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...