protocol is used to place all word registers on the upper word of the data bus (D31-D16).

This is accomplished by asserting DSACK1 and leaving DSACK0 negated when any word

Eegister (other than the register select CIR) is accessed, regardless of the value of A1.

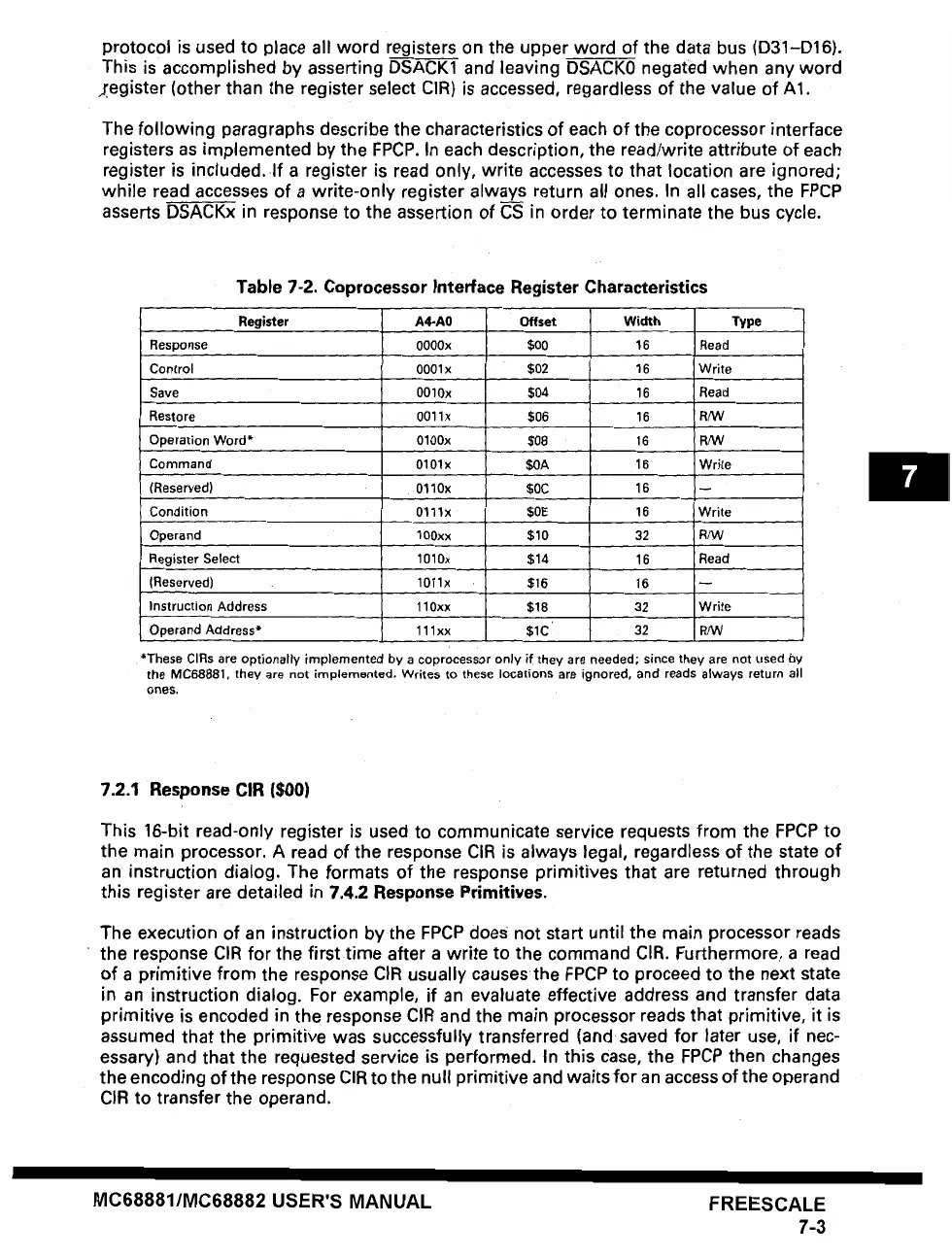

The following paragraphs describe the characteristics of each of the coprocessor interface

registers as implemented by the FPCP. In each description, the read/write attribute of each

register is included. If a register is read only, write accesses to that location are ignored;

while read accesses of a write-only register alway___s return all ones. In all cases, the FPCP

asserts DSACKx in response to the assertion of CS in order to terminate the bus cycle.

Table 7-2. Coprocessor Interface Register Characteristics

Register Width Type

Response

16

Read

Control

16

Write

Save

16

Read

Restore

16 R/W

Operation Word*

16 R/W

Command

16

Write

(Reserved)

16 --

Condition

16

Write

Operand

32 RNV

Register Select

16

Read

(Reserved)

16 --

Instruction Address 32 Write

32 RNV

Operand Address*

A4-A0 Offset

0000x

$00

0001x $02

0010x $O4

0011x $06

0100x $08

0101x $0A

0110x $0C

0111x $0E

100xx $10

1010x $14

1011x $16

110xx $18

111xx $1C

*These CIRs are optionally implemented by a coprocessor only if they are needed; since they are not used by

the MC68881, they

are

not implemented. Writes to these locations are ignored, and reads always return all

ones,

7.2.1 Response CIR ($00)

This 16-bit read-only register is used to communicate service requests from the FPCP to

the main processor. A read of the response CIR is always legal, regardless of the state of

an instruction dialog. The formats of the response primitives that are returned through

this register are detailed in 7.4.2 Response Primitives.

The execution of an instruction by the FPCP does not start until the main processor reads

the response CIR for the first time after a write to the command CIR. Furthermore, a read

of a primitive from the response CIR usually causes the FPCP to proceed to the next state

in an instruction dialog. For example, if an evaluate effective address and transfer data

primitive is encoded in the response CIR and the main processor reads that primitive, it is

assumed that the primitive was successfully transferred (and saved for later use, if nec-

essary) and that the requested service is performed. In this case, the FPCP then changes

the encoding of the response CIR to the null primitive and waits for an access of the operand

CIR to transfer the operand.

MC68881/MC68882 USER'S MANUAL FREESCALE

7-3

Loading...

Loading...