7

7.2.2 Control ClR ($02)

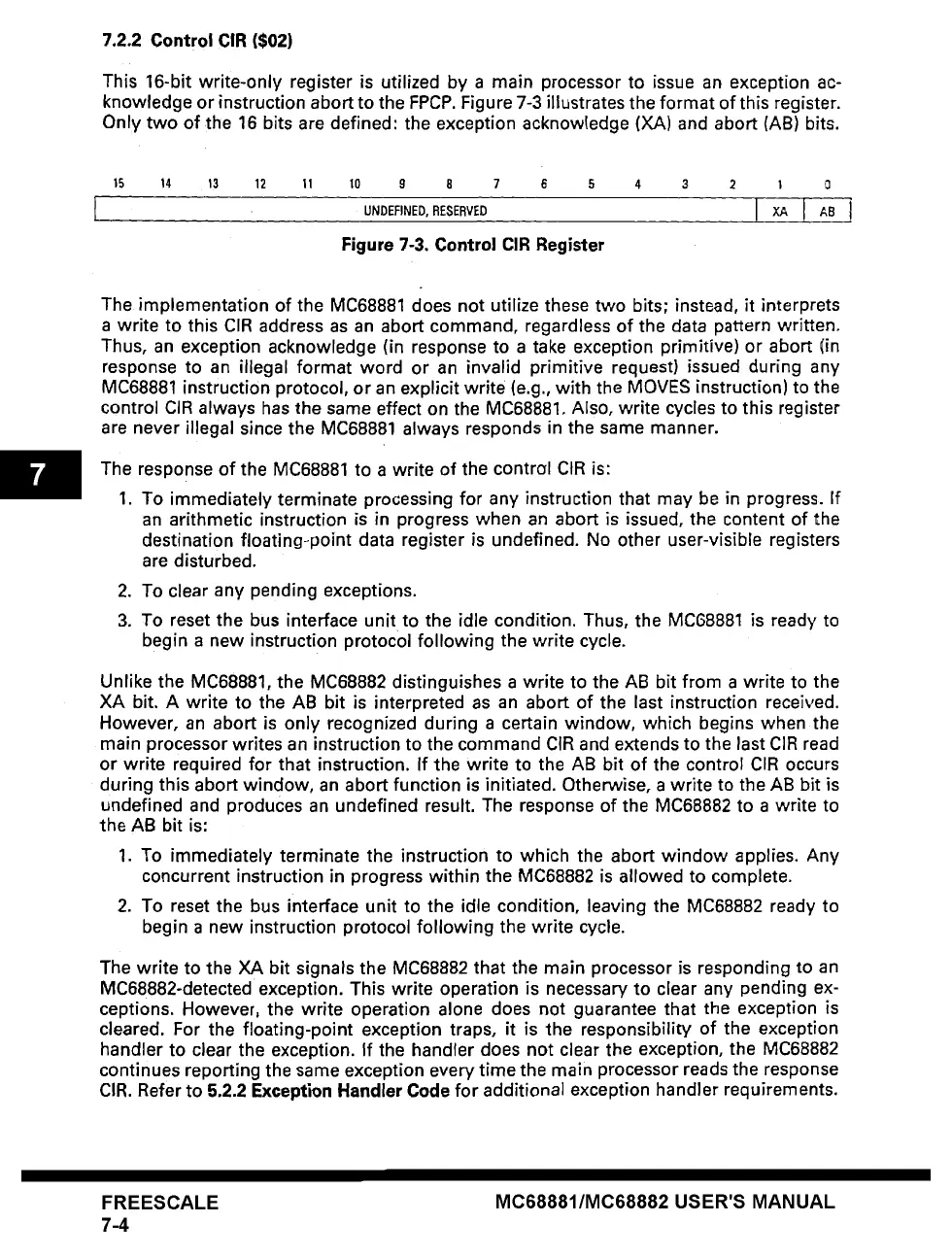

This 16-bit write-only register is utilized by a main processor to issue an exception ac-

knowledge or instruction abort to the FPCP. Figure 7-3 illustrates the format of this register.

Only two of the 16 bits are defined: the exception acknowledge (XA) and abort (AB) bits.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

I UNDEFINED, RESERVED I XA I AB i

Figure 7-3. Control ClR Register

The implementation of the MC68881 does not utilize these two bits; instead, it interprets

a write to this CIR address as an abort command, regardless of the data pattern written.

Thus, an exception acknowledge (in response to a take exception primitive) or abort (in

response to an illegal format word or an invalid primitive request) issued during any

MC68881 instruction protocol, or an explicit write (e.g., with the MOVES instruction) to the

control CIR always has the same effect on the MC68881. Also, write cycles to this register

are never illegal since the MC68881 always responds in the same manner.

The response of the MC68881 to a write of the control CIR is:

1. To immediately terminate processing for any instruction that may be in progress. If

an arithmetic instruction is in progress when an abort is issued, the content of the

destination floating-point data register is undefined. No other user-visible registers

are disturbed.

2. To clear any pending exceptions.

3. To reset the bus interface unit to the idle condition. Thus, the MC68881 is ready to

begin a new instruction protocol following the write cycle.

Unlike the MC68881, the MC68882 distinguishes a write to the AB bit from a write to the

XA bit. A write to the AB bit is interpreted as an abort of the last instruction receh,ed.

However, an abort is only recognized during a certain window, which begins when the

main processor writes an instruction to the command CIR and extends to the last CIR read

or write required for that instruction. If the write to the AB bit of the control CIR occurs

during this abort window, an abort function is initiated. Otherwise, a write to the AB bit is

undefined and produces an undefined result. The response of the MC68882 to a write to

the AB bit is:

1. To immediately terminate the instruction to which the abort window applies. Any

concurrent instruction in progress within the MC68882 is allowed to complete.

2. To reset the bus interface unit to the idle condition, leaving the MC68882 ready to

begin a new instruction protocol following the write cycle.

The write to the XA bit signals the MC68882 that the main processor is responding to an

MC68882-detected exception. This write operation is necessary to clear any pending ex-

ceptions. However, the write operation alone does not guarantee that the exception is

cleared. For the floating-point exception traps, it is the responsibility of the exception

handler to clear the exception. If the handler does not clear the exception, the MC68882

continues reporting the same exception every time the main processor reads the response

CIR. Refer to 5.2.2

Exception Handler Code

for additional exception handler requirements.

FREESCALE

7-4

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...