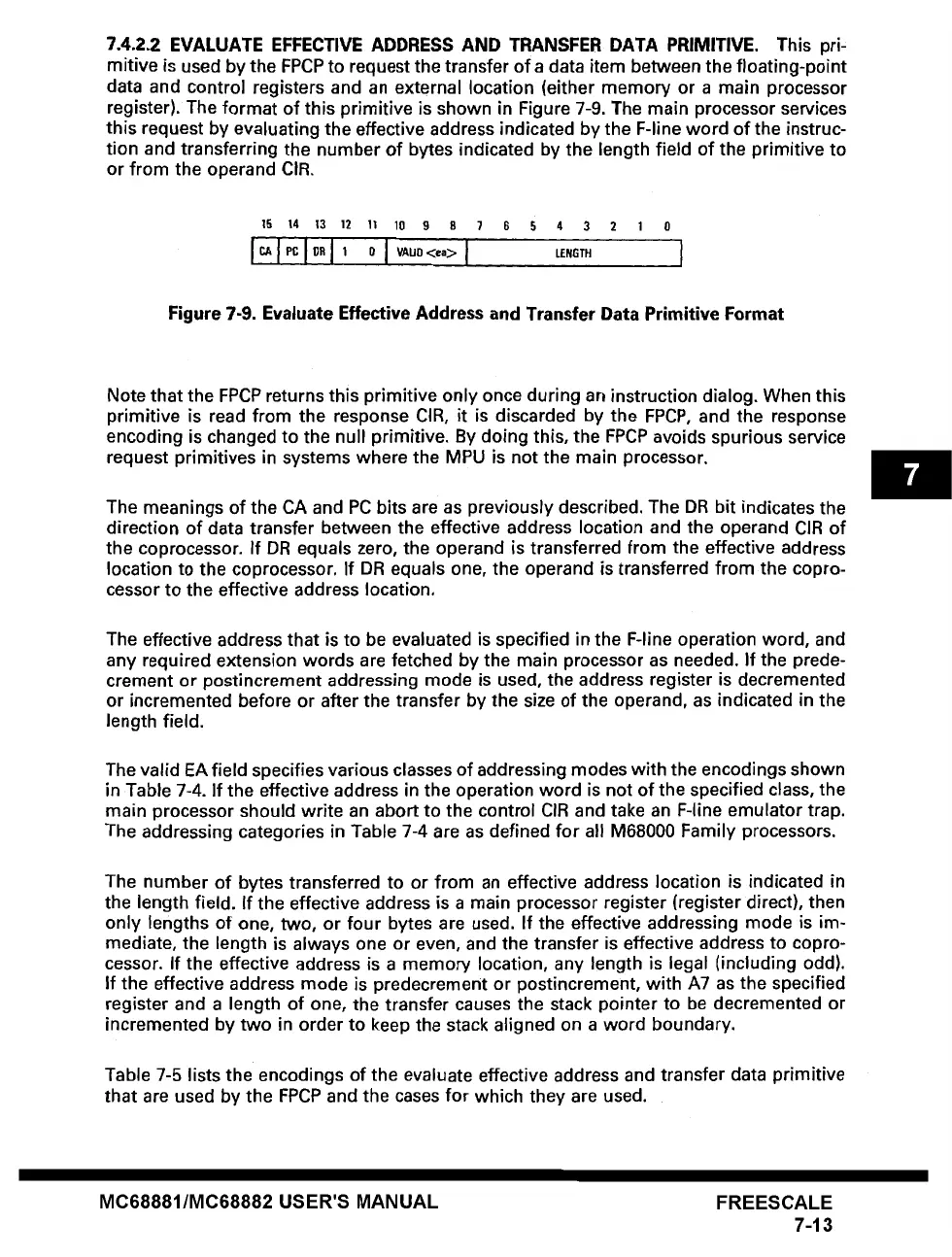

7.4.2.2 EVALUATE EFFECTIVE ADDRESS AND TRANSFER DATA PRIMITIVE.

This pri-

mitive is used by the FPCP to request the transfer of a data item between the floating-point

data and control registers and an external location (either memory or a main processor

register). The format of this primitive is shown in Figure 7-9, The main processor services

this request by evaluating the effective address indicated by the F-line word of the instruc-

tion and transferring the number of bytes indicated by the length field of the primitive to

or from the operand CIR.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 O

Figure 7-9. Evaluate Effective Address and Transfer Data Primitive Format

Note that the FPCP returns this primitive only once during an instruction dialog. When this

primitive is read from the response CIR, it is discarded by the FPCP, and the response

encoding is changed to the null primitive. By doing this, the FPCP avoids spurious service

request primitives in systems where the MPU is not the main processor.

The meanings of the CA and PC bits are as previously described. The DR bit indicates the

direction of data transfer between the effective address location and the operand CIR of

the coprocessor. If DR equals zero, the operand is transferred from the effective address

location to the coprocessor. If DR equals one, the operand is transferred from the copro-

cessor to the effective address location.

The effective address that is to be evaluated is specified in the F-line operation word, and

any required extension words are fetched by the main processor as needed. If the prede-

crement or postincrement addressing mode is used, the address register is decremented

or incremented before or after the transfer by the size of the operand, as indicated in the

length field.

The valid EA field specifies various classes of addressing modes with the encodings shown

in Table 7-4. If the effective address in the operation word is not of the specified class, the

main processor should write an abort to the control CIR and take an F-line emulator trap.

The addressing categories in Table 7-4 are as defined for all M68000 Family processors.

The number of bytes transferred to or from an effective address location is indicated in

the length field. If the effective address is a main processor register (register direct), then

only lengths of one, two, or four bytes are used. If the effective addressing mode is im-

mediate, the length is always one or even, and the transfer is effective address to copro-

cessor. If the effective address is a memory location, any length is legal (including odd).

If the effective address mode is predecrement or postincrement, with A7 as the specified

register and a length of one, the transfer causes the stack pointer to be decremented or

incremented by two in order to keep the stack aligned on a word boundary.

Table 7-5 lists the encodings of the evaluate effective address and transfer data primitive

that are used by the FPCP and the cases for which they are used.

MC68881/MC68882 USER'S MANUAL

FREESCALE

7-13

Loading...

Loading...