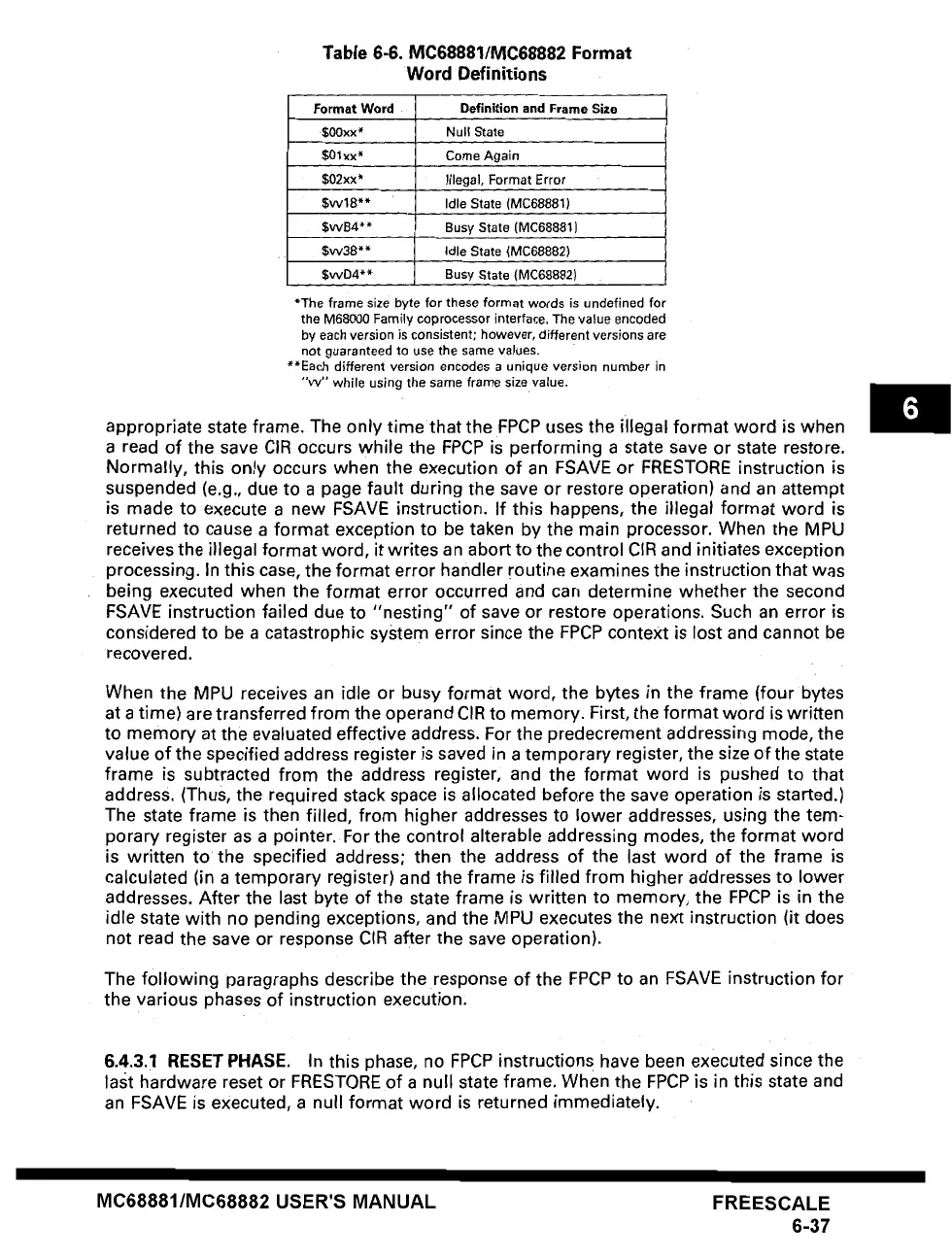

Table 6-6. MC68881/MC68882 Format

Word Definitions

Format Word Definition and Frame Size

$O0xx* Null State

$01xx* Come Again

$02xx* Illegal, Format Error

$w18"* Idle State (MC68881)

$wB4** Busy State (MC68881)

$w3B** Idle State (MC68882)

$wD4** Busy State (MC68882)

*The frame size byte for these format words is undefined for

the M68000 Family coprocessor interface. The value encoded

by each version is consistent; however, different versions are

not guaranteed to use the same values.

**Each different version encodes a unique version number in

"vv" while using the same frame size value.

appropriate state frame. The only time that the FPCP uses the illegal format word is when

a read of the save CIR occurs while the FPCP is performing a state save or state restore.

Normally, this only occurs when the execution of an FSAVE or FRESTORE instruction is

suspended (e.g., due to a page fault during the save or restore operation) and an attempt

is made to execute a new FSAVE instruction. If this happens, the illegal format word is

returned to cause a format exception to be taken by the main processor. When the MPU

receives the illegal format word, it writes an abort to the control CIR and initiates exception

processing. In this case, the format error handler routine examines the instruction that was

being executed when the format error occurred and can determine whether the second

FSAVE instruction failed due to "nesting" of save or restore operations. Such an error is

considered to be a catastrophic system error since the FPCP context is lost and cannot be

recovered.

When the MPU receives an idle or busy format word, the bytes in the frame (four bytes

at a time) are transferred from the operand CIR to memory. First, the format word is written

to memory at the evaluated effective address. For the predecrement addressing mode, the

value of the specified address register is saved in a temporary register, the size of the state

frame is subtracted from the address register, and the format word is pushed to that

address. (Thus, the required stack space is allocated before the save operation is started.)

The state frame is then filled, from higher addresses to lower addresses, using the tem-

porary register as a pointer. For the control alterable addressing modes, the format word

is written to the specified address; then the address of the last word of the frame is

calculated (in a temporary register) and the frame is filled from higher addresses to lower

addresses. After the last byte of the state frame is written to memory, the FPCP is in the

idle state with no pending exceptions, and the MPU executes the next instruction (it does

not read the save or response CIR after the save operation).

The following paragraphs describe the response of the FPCP to an FSAVE instruction for

the various phases of instruction execution,

6.4.3.1 RESET PHASE. In this phase, no FPCP instructions have been executed since the

last hardware reset or FRESTORE of a null state frame, when the FPCP is in this state and

an FSAVE is executed, a null format word is returned immediately.

MC68881/MC68882 USER'S MANUAL FREESCALE

6-37

Loading...

Loading...