6

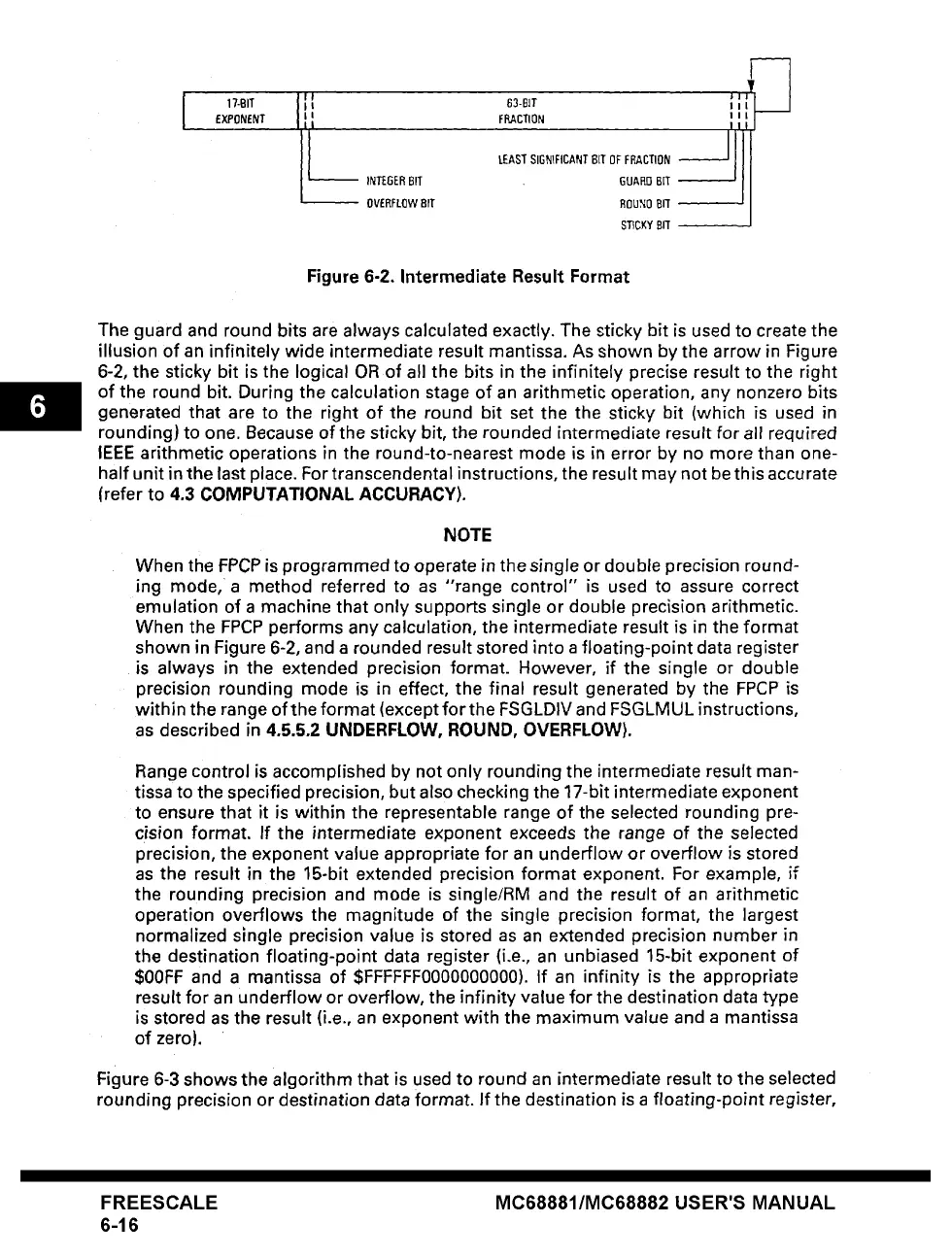

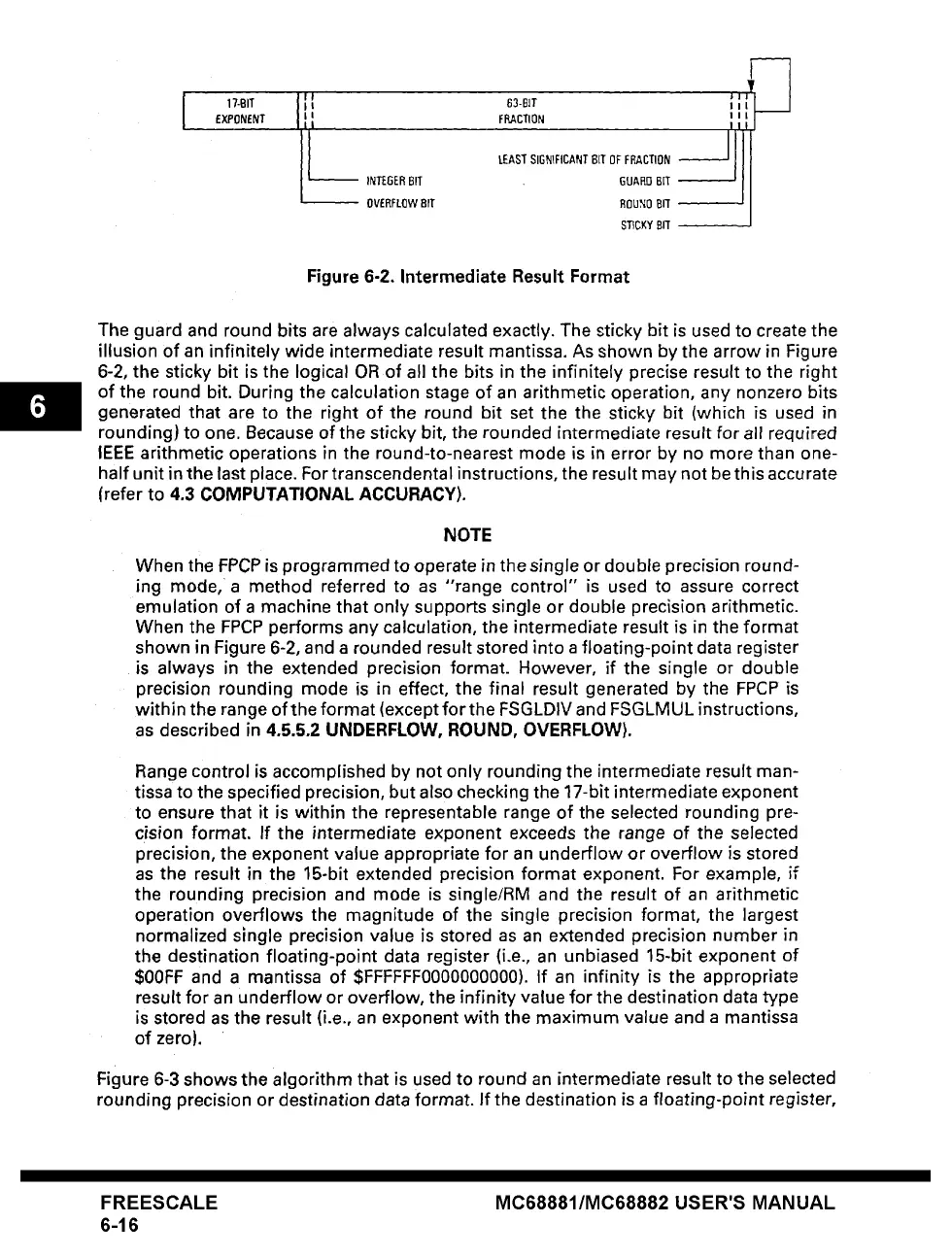

17-BIT

EXPONENT

IL

@3-B}T

FRACTION

LEAST SI6N1FICANT BET OF FRACTION --

INTEGER BIT GUARD BET --

-- OVERFLOW BIT ROU,~D BIT --

S~CKY BE --

Ill

III

Figure 6-2, Intermediate Result Format

The guard and round bits are always calculated exactly. The sticky bit is used to create the

illusion of an infinitely wide intermediate result mantissa. As shown by the arrow in Figure

6-2, the sticky bit is the logical OR of all the bits in the infinitely precise result to the right

of the round bit. During the calculation stage of an arithmetic operation, any nonzero bits

generated that are to the right of the round bit set the the sticky bit (which is used in

rounding) to one. Because of the sticky bit, the rounded intermediate result for all required

IEEE arithmetic operations in the round-to-nearest mode is in error by no more than one-

half unit in the last place. For transcendental instructions, the result may not be this accurate

(refer to 4.3 COMPUTATIONAL ACCURACY).

NOTE

When the FPCP is programmed to operate in the single or double precision round-

ing mode, a method referred to as "range control" is used to assure correct

emulation of a machine that only supports single or double precision arithmetic.

When the FPCP performs any calculation, the intermediate result is in the format

shown in Figure 6-2, and a rounded result stored into a floating-point data register

is always in the extended precision format. However, if the single or double

precision rounding mode is in effect, the final result generated by the FPCP is

within the range of the format (except for the FSGLDIV and FSGLMUL instructions,

as described in 4.5.5.2 UNDERFLOW, ROUND, OVERFLOW).

Range control is accomplished by not only rounding the intermediate result man-

tissa to the specified precision, but also checking the 17-bit intermediate exponent

to ensure that it is within the representable range of the selected rounding pre-

cision format. If the intermediate exponent exceeds the

range

of the selected

precision, the exponent value appropriate for an underflow or overflow is stored

as the result in the 15-bit extended precision format exponent. For example, if

the rounding precision and mode is single/RM and the result of an arithmetic

operation overflows the magnitude of the single precision format, the largest

normalized single precision value is stored as an extended precision number in

the destination floating-point data register (i.e., an unbiased 15-bit exponent of

$00FF and a mantissa of $FFFFFF0000000000). If an infinity is the appropriate

result for an underflow or overflow, the infinity value for the destination data type

is stored as the result (i.e., an exponent with the maximum value and a mantissa

of zero).

Figure 6-3 shows the algorithm that is used to round an intermediate result to the selected

rounding precision or destination

data

format. If the destination is a floating-point register,

FREESCALE

6-16

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...