that since this instruction type cannot cause an exception, the PC bit is not set in any

primitive; thus, these instructions can be used to read or write the control registers without

overwriting the FPIAR contents.

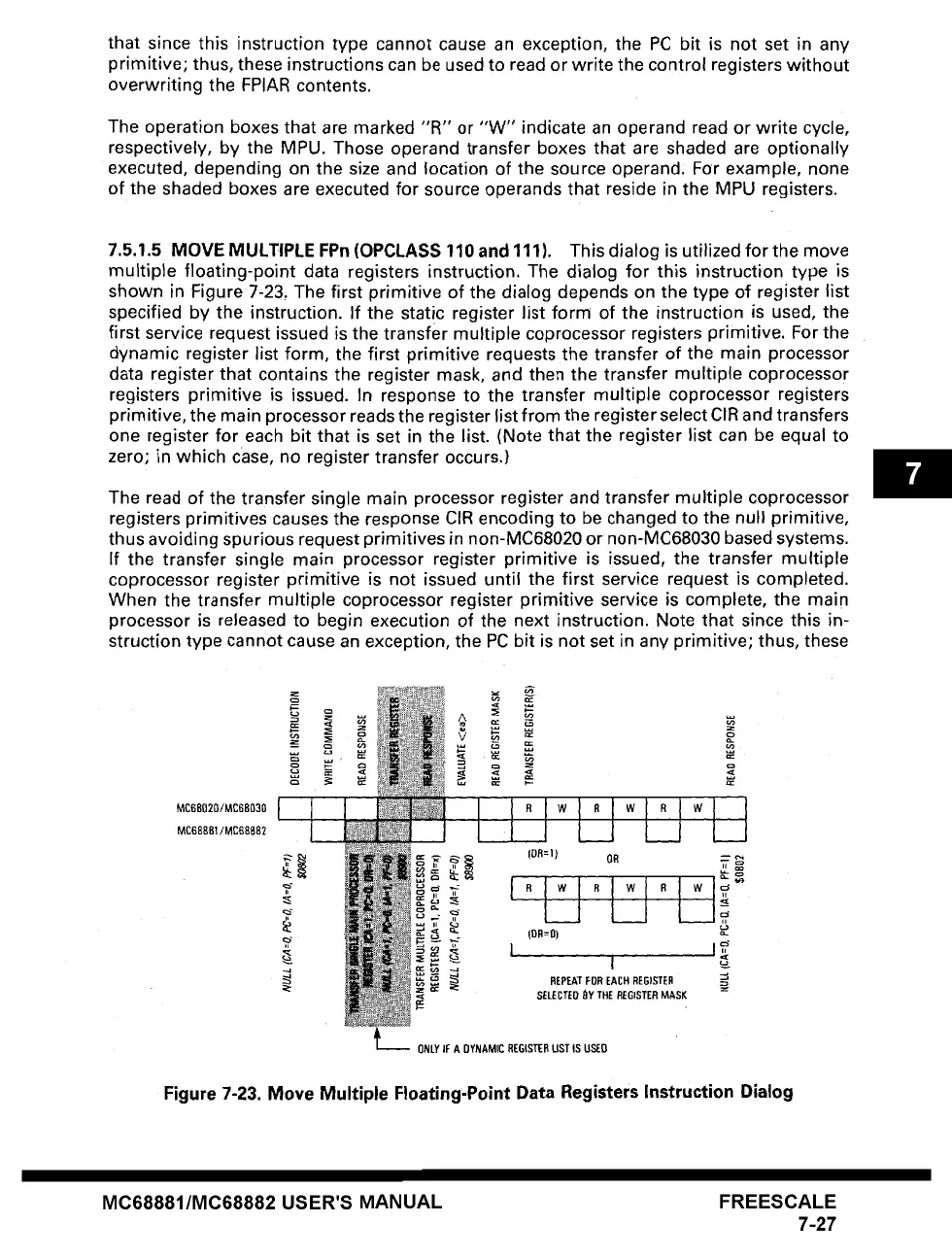

The operation boxes that are marked

"R"

or

"W"

indicate an operand read or write cycle,

respectively, by the MPU. Those operand transfer boxes that are shaded are optionally

executed, depending on the size and location of the source operand, For example, none

of the shaded boxes are executed for source operands that reside in the MPU registers.

7.5.1.5 MOVE MULTIPLE FPn (OPCLASS 110 and 111). This dialog is utilized for the move

multiple floating-point data registers instruction. The dialog for this instruction type is

shown in Figure 7-23, The first primitive of the dialog depends on the type of register list

specified by the instruction. If the static register list form of the instruction is used, the

first service request issued is the transfer multiple coprocessor registers primitive. For the

dynamic register list form, the first primitive requests the transfer of the main processor

data register that contains the register mask, and then the transfer multiple coprocessor

registers primitive is issued. In response to the transfer multiple coprocessor registers

primitive, the main processor reads the register list from the register select CIR and transfers

one register for each bit that is set in the list. (Note that the register list can be equal to

zero; in which case, no register transfer occurs.)

The read of the transfer single main processor register and transfer multiple coprocessor

registers primitives causes the response CIR encoding to be changed to the null primitive,

thus avoiding spurious request primitives in non-MC68020 or non-MC68030 based systems.

If the transfer single main processor register primitive is issued, the transfer multiple

coprocessor register primitive is not issued until the first service request is completed.

When the transfer multiple coprocessor register primitive service is complete, the main

processor is released to begin execution of the next instruction. Note that since this in-

struction type cannot cause an exception, the PC bit is not set in any primitive; thus, these

MC68020/MC68G31]

MC68881/MC68882

~- N ~--- ~ (DR=0) =-

--a m,j~ ..j v

~E SELECTED ~IY T.E REGISTER MASK

~ ~ REPEAT FOR EACH REGISTER

-- 0NLY IF A DYNAMIC REGISTER LIST IS USED

Figure 7-23. Move Multiple Floating-Point Data Registers Instruction Dialog

MC68881/MC68882 USER'S MANUAL

FREESCALE

7-27

Loading...

Loading...