7

instructions can be used to read the floating-point data registers without overwriting the

FPIAR contents.

The operation boxes that are marked "R" and "W" indicate an operand read or write cycle,

respectively, by the MPU.

7.5.2 Conditional Instructions

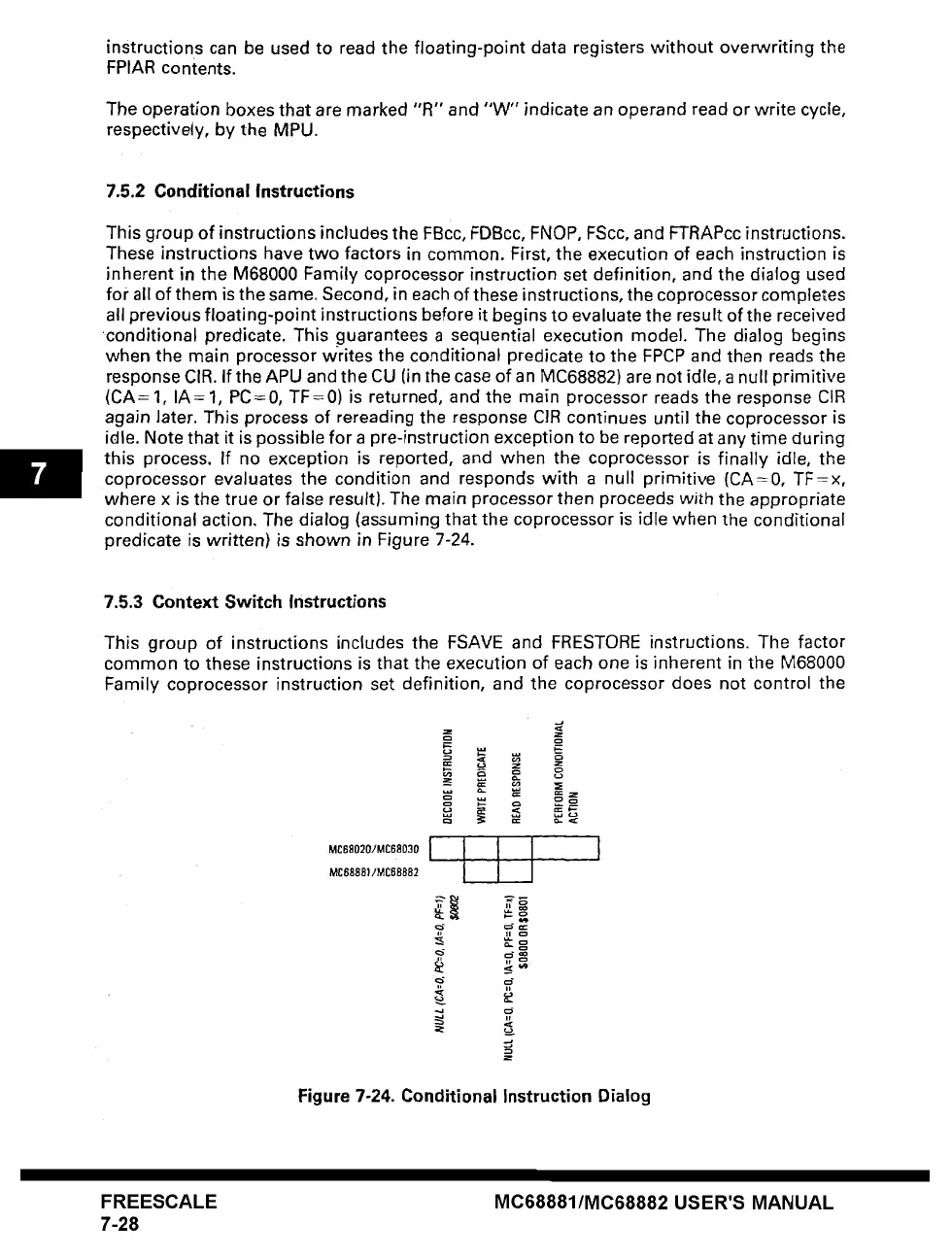

This group of instructions includes the FBcc, FDBcc, FNOP, FScc, and FTRAPcc instructions.

These instructions have two factors in common. First, the execution of each instruction is

inherent in the M68000 Family coprocessor instruction set definition, and the dialog used

for all of them is the same. Second, in each of these instructions, the coprocessor completes

all previous floating-point instructions before it begins to evaluate the result of the received

conditional predicate. This guarantees a sequential execution model. The dialog begins

when the main processor writes the conditional predicate to the FPCP and then reads the

response CIR. If the APU and the CU (in the case of an MC68882) are not idle, a null primitive

(CA= 1, IA=I, PC=0, TF=0) is returned, and the main processor reads the response CIR

again later. This process of rereading the response CIR continues until the coprocessor is

idle. Note that it is possible for a pre-instruction exception to be reported at any time during

this process. If no exception is reported, and when the coprocessor is finally idle, the

coprocessor evaluates the condition and responds with a null primitive (CA=0, TF=x,

where x is the true or false result). The main

processor then proceeds with the appropriate

conditional action. The dialog (assuming that the coprocessor is idle when the conditional

predicate is written) is shown in Figure 7-24.

7.5.3 Context Switch Instructions

This group of instructions includes the FSAVE and FRESTORE instructions. The factor

common to these instructions is that the execution of each one is inherent in the M68000

Family coprocessor instruction set definition, and the coprocessor does not control the

MC68020/MC68030

MC6888|/MC688B2

o

o

7=

Figure 7-24. Conditional Instruction Dialog

FREESCALE

7-28

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...