79 63

FPO

FPI

FP"2

FF'3

~4

~5

FP6

FP7

31 23 15 7 O

.... : ....

IEXCEPTIDNI MOOE , ~_

.... E .... I E.~R~ I c0.~0~ I

FPC" (~t'TP~L~ER

CONDITION n.n~cu'r EXCEFIION ACCRUED -]._

CODE .........

STATUS EXCEFIION FPSR STATICS RE 0'3TER

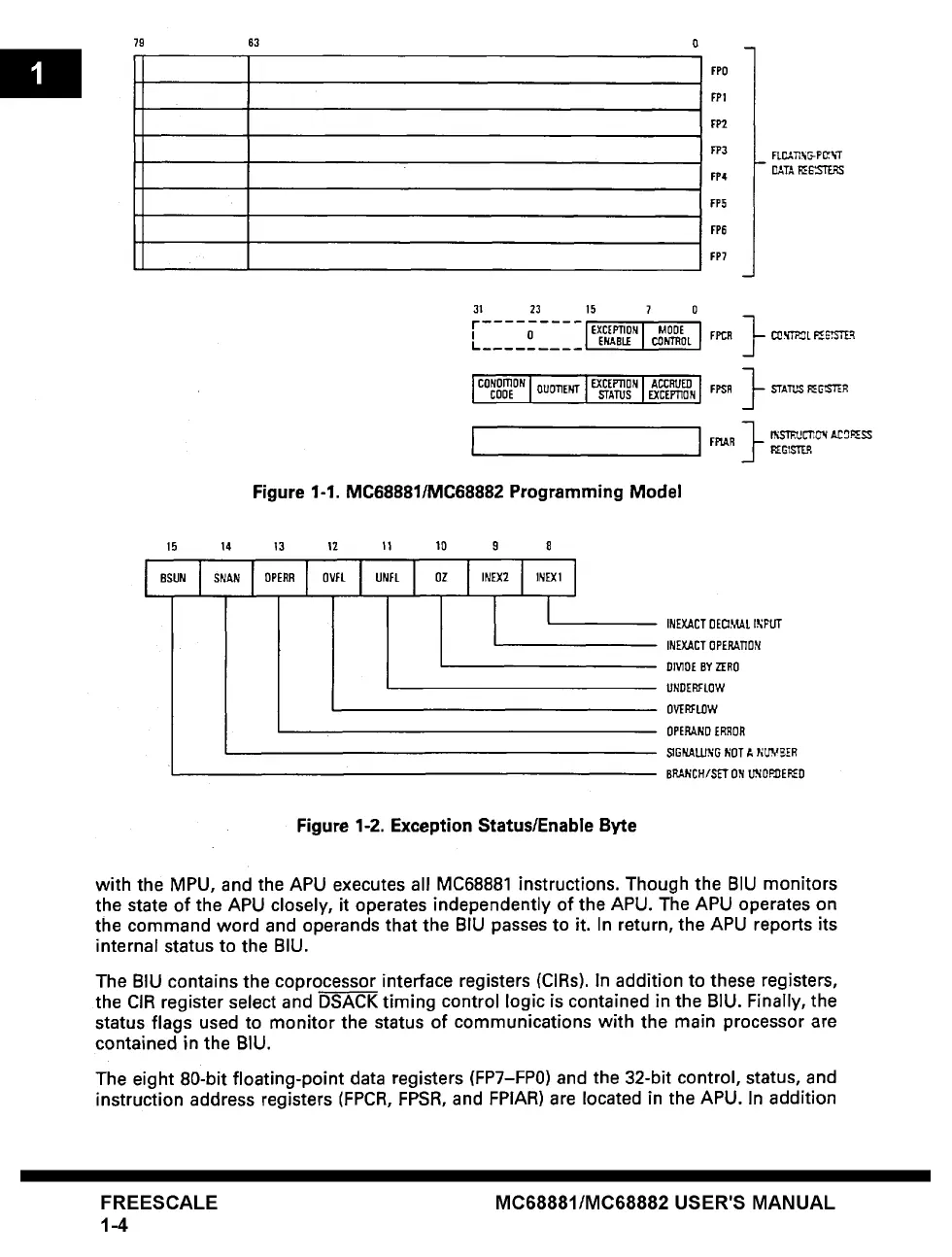

Figure 1-1. MC68881/MC68882 Programming Model

15 14 13 12 11 10

~,' N I SN~,N I OPERR [ OVFL I UNFL I DZ

I INEX2

8

I

i

INEXACT D EC~,=,'~L t~FgT

INEXACT OPERATION

DIV1DE BY ZERO

UNDERFLOW

OVERFLOW

OPERAND ERROR

SIGNALUNG NOT A ~I;L~M~ER

BRANCH/SET ON U~O.~'~EFED

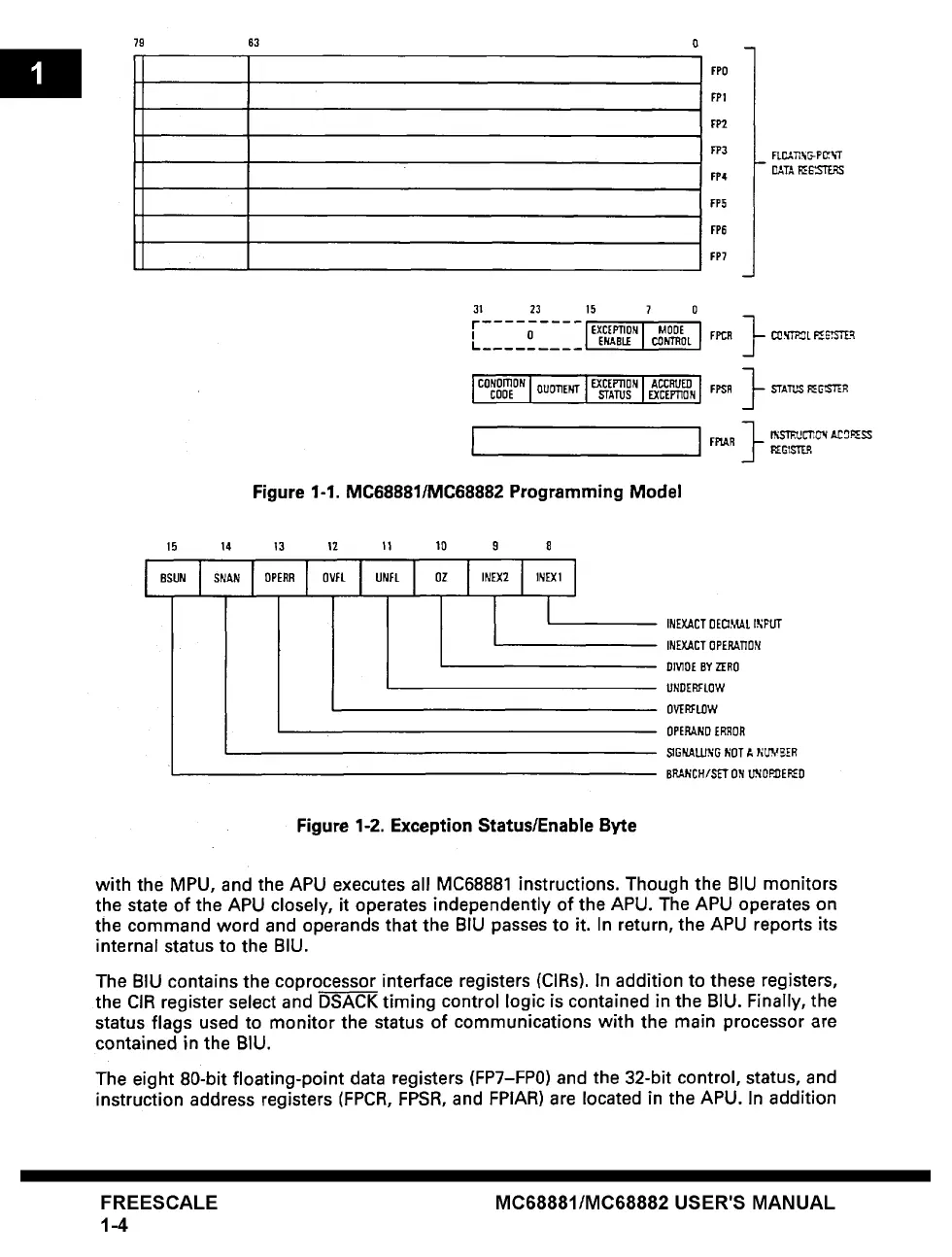

Figure 1-2. Exception Status/Enable Byte

with the MPU, and the APU executes all MC68881 instructions. Though the BIU monitors

the state of the APU closely, it operates independently of the APU. The APU operates on

the command word and operands that the BIU passes to it. In return, the APU reports its

internal status to the BIU.

The BIU contains the coprocessor interface registers (CIRs). In addition to these registers,

the CIR register select and DSACK timing control logic is contained in the BIU. Finally, the

status flags used to monitor the status of communications with the main processor are

contained in the BIU.

The eight 80-bit floating-point data registers (FP7-FP0) and the 32-bit control, status, and

instruction address registers (FPCR, FPSR, and FPIAR) are located in the APU. In addition

FREESCALE

1-4

MC68881/MC68882 USER'S MANUAL

Loading...

Loading...