SECTION 7

COPROCESSOR INTERFACE

This section describes the coprocessor interface with respect to the communication pro-

tocol utilized by the MC68881/MC68882 (FPCP) and MC68020/MC68030 (MPU). This com-

munication protocol includes electrical and command-level mechanisms that allow a

coprocessor to act as an extension to the main processor.

The connection between the MPU and the FPCP is an extension of the M68000 bus interface,

with the FPCP connected as an auxiliary device to the MPU. The FPCP is selected by a

chip-select (C--S) signal that is decoded from the MPU function code and address bus lines.

The FPCP contains a set of coprocessor interface registers (CIRs) by which the main pro-

cessor and coprocessor communicate. These registers are not related to the programming

model implemented by the FPCP. Rather, they are used as communication ports that have

specific functions associated with each register. When the FPCP is used as a coprocessor

to the MPU, the programmer is never required to explicitly access these interface registers,

since the coprocessor interface is implemented in the hardware and microcode of the MPU.

A main processor other than an MPU explicitly accesses the FPCP CIRs using a software

routine that simulates the behavior of the MPU with respect to the coprocessor interface.

For more information on the electrical interconnecti0n between the main processor and

the FPCP, refer to SECTION 11 INTERFACING

METHODS.

7.1 CHIP-SELECT DECODE

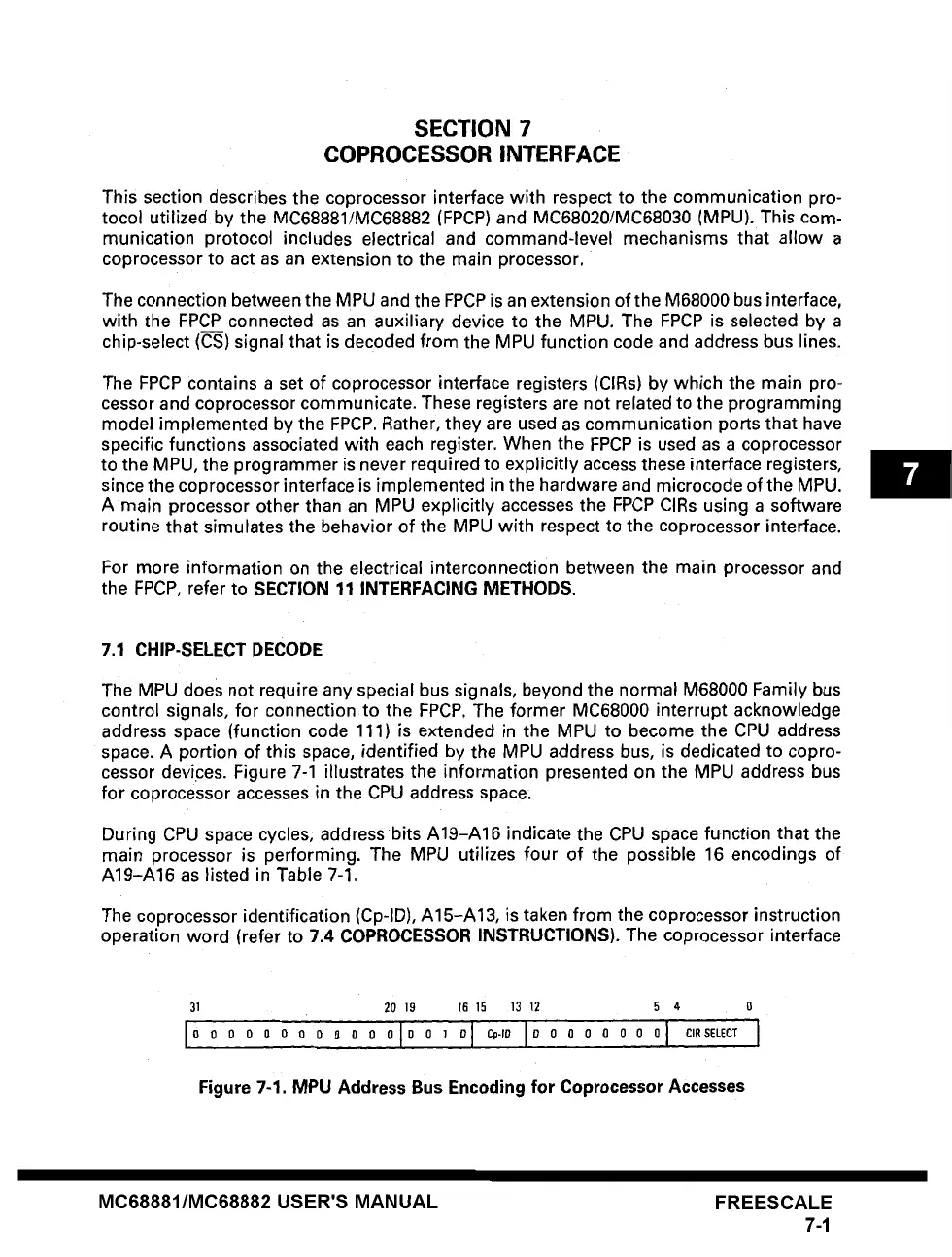

The MPU does not require any special bus signals, beyond the normal M68000 Family bus

control signals, for connection to the FPCP. The former MC68000 interrupt acknowledge

address space (function code 111) is extended in the MPU to become the CPU address

space. A portion of this space, identified by the MPU address bus, is dedicated to copro-

cessor devices. Figure 7-1 illustrates the information presented on the MPU address bus

for coprocessor accesses in the CPU address space:

During CPU space cycles, addressbits A19-A16 indicate the CPU space function that the

main processor is performing. The MPU utilizes four of the possible 16 encodings of

A19-A16 as listed in Table 7-1.

The coprocessor identification (Cp-ID), A15-A13, is taken from the coprocessor instruction

operation word (refer to 7.4 COPROCESSOR INSTRUCTIONS). The coprocessor interface

31 20 19 16 15 13 12 5 4 0

Figure 7-1. MPU Address Bus Encoding for Coprocessor Accesses

MC68881/MC68882 USER'S MANUAL FREESCALE

7-1

Loading...

Loading...